# Mixed Criticality Systems - A Review\*

Alan Burns and Robert I. Davis

Department of Computer Science,

University of York, York, UK.

email: {alan.burns, rob.davis}@york.ac.uk

#### **Abstract**

This review covers research on the topic of mixed criticality systems that has been published since Vestal's 2007 paper. It covers the period up to and including July 2018. The review is organised into the following topics: introduction and motivation, models, single processor analysis (including job-based, hard and soft tasks, fixed priority and EDF scheduling, shared resources and static and synchronous scheduling), multiprocessor analysis, related topics, realistic models, formal treatments, systems issues and industrial practice.

<sup>\*</sup>eleventh edition, August 2018.

# **Contents**

| 1 | Intr                      | oduction                                      | 4  |

|---|---------------------------|-----------------------------------------------|----|

| 2 | Mixed Criticality Models  |                                               |    |

| 3 | Single Processor Analysis |                                               |    |

|   | 3.1                       | Job scheduling                                | 8  |

|   | 3.2                       | Fixed Priority Scheduling                     | 9  |

|   |                           | 3.2.1 RTA-Based approaches                    | 9  |

|   |                           | 3.2.2 Slack scheduling                        | 13 |

|   |                           | 3.2.3 Period transformation                   | 14 |

|   | 3.3                       | EDF Scheduling                                | 15 |

|   | 3.4                       | Shared Resources                              | 17 |

|   | 3.5                       | Static and Synchronous Scheduling             | 18 |

|   | 3.6                       | Varying Speed Processors                      | 19 |

| 4 | Mul                       | tiprocessor Analysis                          | 19 |

|   | 4.1                       | Task Allocation                               | 20 |

|   | 4.2                       | Schedulability Analysis                       | 22 |

|   | 4.3                       | Communication and other Resources             | 22 |

| 5 | Linl                      | ks to other Research Topics                   | 26 |

|   | 5.1                       | Hard and Soft Tasks                           | 26 |

|   | 5.2                       | Fault Tolerant Systems (FTS)                  | 28 |

|   | 5.3                       | Security                                      | 29 |

|   | 5.4                       | Hierarchical Scheduling                       | 29 |

|   | 5.5                       | Cyber Physical Systems and Internet of Things | 30 |

|   | 5.6                       | Probabilistic real-time systems               | 31 |

| 6 | Mor                       | re Realistic MCS Models                       | 33 |

| 7 | Mor                       | re Formal Treatments                          | 37 |

|   | 7.1                       | Utilisation Bounds                            | 37 |

|   | 7.2                       | Speedup Factors                               | 37 |

|   | 7.3                       | Formal Language and Modelling Issues          | 38 |

| 8 | Systems Issues            |                                               | 39 |

| 9 | Indi                      | istry Practice and Standards                  | 44 |

| 10 PhD Awards for Research within the Field of MCS | 45 |

|----------------------------------------------------|----|

| 11 Conclusion and Directions for Future Work       | 46 |

# 1 Introduction

An increasingly important trend in the design of real-time and embedded systems is the integration of components with different levels of criticality onto a common hardware platform. At the same time, these platforms are migrating from single cores to multi-cores and in the future many-core architectures. Criticality is a designation of the level of assurance against failure needed for a system component. A mixed criticality system (MCS) is one that has two or more distinct levels (for example safety critical, mission critical and low-critical). Perhaps up to five levels may be identified (see, for example, the IEC 61508, DO-178B and DO-178C, DO-254 and ISO 26262 standards). Typical names for the levels are ASILs (Automotive Safety and Integrity Levels), DALs (Design Assurance Levels or Development Assurance Levels) and SILs (Safety Integrity Levels). It should be noted that not all standards and papers on MCS assign the same meaning to 'criticality', an issue explored by Graydon and Bate [204], Esper et al. [173], Paulitsch et al. [374] and Ernst and Di Natale [172].

Most of the complex embedded systems found in, for example, the automotive and avionics industries are evolving into mixed criticality systems in order to meet stringent non-functional requirements relating to cost, space, weight, heat generation and power consumption (the latter being of particular relevance to mobile systems). Indeed the software standards in the European automotive industry (AUTOSAR<sup>1</sup>) and in the avionics domain (ARINC<sup>2</sup>) address mixed criticality issues; in the sense that they recognise that MCS must be supported on their platforms.

The fundamental research question underlying these initiatives and standards is: how, in a disciplined way, to reconcile the conflicting requirements of *partitioning* for (safety) assurance and *sharing* for efficient resource usage. This question gives rise to theoretical problems in modelling and verification, and systems problems relating to the design and implementation of the necessary hardware and software run-time controls.

A key aspect of MCS is that system parameters, such as tasks' worst-case execution times (WCETs), become dependent on the criticality level of the tasks. So the same code will have a higher WCET if it is defined to be safety-critical (as a higher level of assurance is required) than it would if it is just considered to be mission critical or indeed non-critical. This property of MCS significantly modifies/undermines many of the standard scheduling results. This report aims to review the research that has been published on MCS.

The first paper on the verification of a Mixed Criticality System used an exten-

<sup>1</sup>http://www.autosar.org/

<sup>&</sup>lt;sup>2</sup>http://www.arinc.com/

sion of standard fixed priority (FP) real-time scheduling theory, and was published by Vestal (of Honeywell Aerospace) in 2007 [451]<sup>3</sup>. It employed a somewhat restrictive work-flow model, focused on a single processor and made use of Response Time Analysis [28]. It showed that neither rate monotonic [319] nor deadline monotonic [304] priority assignment is optimal for MCS; however Audsley's optimal priority assignment algorithm [26] was found to be applicable.

This paper was followed by two publications in 2008 by Baruah and Vestal [75], and Huber et al. [255]. The first of these papers generalises Vestal's model by using a sporadic task model and by assessing fixed job-priority scheduling and dynamic priority scheduling. It contains the important result that EDF (Earliest Deadline First) does not dominate FP when criticality levels are introduced, and that there are feasible systems that cannot be scheduled by EDF. The latter paper addresses multi-processor issues and virtualisation (though it did not use that term). It focused on AUTOSAR and resource management (encapsulation and monitoring) with time-triggered applications and a trusted network layer.

Further impetus to defining MCS as a distinct research topic came from the white paper produced by Barhorst et al. [40], the keynote talk that Baruah gave at the 2010 ECRTS conference<sup>4</sup> and a workshop report from the European Commission [441]. These have been followed up by tutorials on MCS at ESWEEK in 2012 and 2013<sup>5</sup>, a workshop at HiPEAC in January 2013<sup>6</sup>, a workshop (WICERT) at DATE 2013<sup>7</sup>, a workshop (ReTiMiCS) at RTCSA 2013<sup>8</sup>, workshops (WMC) at RTSS 2013<sup>9</sup>, RTSS 2014<sup>10</sup>, RTSS 2015<sup>11</sup>, RTSS 2016<sup>12</sup> and RTSS 2017<sup>13</sup>; a workshop at the 19th International Conference on Reliable Software Technologies (Ada-Europe) in June 2014, and Dagstuhl Seminars on Mixed Criticality and Many

<sup>&</sup>lt;sup>3</sup>The term Mixed Criticality had been used before 2007 to address issues of non-interference in non-federated architectures such as IMA [239]; Vestal changed the focus of research by concentrating on real-time performance. Systems with more than one criticality level but aim to only give complete isolation are called *multiple-criticality systems*; the use of *mixed-criticality* implies some tradeoff between isolation and integration that involves resource sharing.

<sup>&</sup>lt;sup>4</sup>Available from the conference web site: http://ecrts.eit.uni-kl.de/index.php?id=53.

<sup>&</sup>lt;sup>5</sup>Embedded Systems Week: http://www.esweek.org/

<sup>&</sup>lt;sup>6</sup>http://www.hipeac.net/conference/berlin/workshop/integration-mixed-criticality-subsystems-multi-core-processors

<sup>&</sup>lt;sup>7</sup>http://atcproyectos.ugr.es/wicert/index.php/conference-proceedings

<sup>8</sup>http://igm.univ-mlv.fr/rtalgo/Events/RETIMICS/

<sup>9</sup>http://www.cs.york.ac.uk/ robdavis/wmc2013/

<sup>10</sup>http://www.cs.york.ac.uk/robdavis/wmc2014/

<sup>11</sup>http://www.cs.york.ac.uk/ robdavis/wmc/

<sup>&</sup>lt;sup>12</sup>https://gsathish.github.io/wmc2016/

<sup>&</sup>lt;sup>13</sup>https://cps-research-group.github.io/WMC2017/

Core Platforms in 2015<sup>14</sup> and 2017<sup>15</sup>.

This review [103] is organised as follows. In Section 2 we first consider mixed criticality models. Then in Section 3 single processor systems are covered (including fixed priority and EDF scheduling). Section 4 covers multiprocessor issues and Section 5 links this research to other topics such as hard and soft real-time scheduling and hierarchical scheduling. More realistic models are covered in Section 6, more formal work is covered in Section 7 and systems work is covered in Section 8. Industry practice and safety standards provide a somewhat different perspective on MCS to Vestal's model; these differences are discussed in Section 9. Section 10 lists PhD dissertations that have been produced on MCS since 2014. The review concludes with Section 11 which outlines a number of open problems and areas where further research is needed.

An adaptation of this review, covering publications up to the end of 2016, has been published in ACM Computer Surveys [105]. This should be used as the main citation for this report. Other overviews/surveys on MCS have also been produced [21,220].

# 2 Mixed Criticality Models

Inevitably not all papers on mixed criticality have used the same system or task model. Here we define a model that is generally applicable and is capable of describing the main results considered in this review.

A system is defined as a finite set of components K. Each component has a level of criticality (designated by the systems engineer responsible for the entire system), L, and contains a finite set of *sporadic tasks*. Each task,  $\tau_i$ , is defined by its period (minimum arrival interval), deadline, computation time and criticality level:  $(T_i, D_i, C_i, L_i)$ . Tasks give rise to a potentially unbounded sequence of *jobs*.

The primary concern with the implementation of MCS is one of separation. Tasks from different components must not be allowed to interfere with each other. In particular, mechanisms must be in place to prevent a job from executing for more than the computation time C defined for its task, and to ensure that a task does not generate jobs that are closer together than  $T^{16}$ .

The requirement to protect the operation of one component from the faults of another is present in all systems that host multiple applications. It is however of particular significance if components have different criticality levels. Since without

<sup>14</sup>http://www.dagstuhl.de/15121

<sup>15</sup> http://www.dagstuhl.de/17131

<sup>&</sup>lt;sup>16</sup>Or (period minus release jitter) if that is part of the task model.

such protection, all components would need to be engineered to the strict standards of the highest criticality level, potentially massively increasing development costs.

After concerns of partitioning comes the need to use resources efficiently. This is facilitated by noting that the task parameters are not independent, in particular the worst-case computation/execution time estimate,  $C_i$ , will be derived by a process dictated by the criticality level. The higher the criticality level, the more conservative the verification process and hence the greater will be the value of  $C_i$ . This was the observation at the heart of the paper by Vestal [451].

For systems executing on hardware platforms with deterministic behaviour, any particular task will have a single real WCET (worst-case execution time); however, this value typically cannot be known with complete certainty. This uncertainty is primarily epistemic (uncertainty in what we know, or do not know, about the system) rather than aleatory (uncertainty in the system itself). Although it is reasonable to assume confidence increases (i.e. uncertainty decreases) with larger estimates of worst-case execution time, this may not be universally true [204]. It would certainly be hard to estimate what increase in confidence would result from, say, a 10% increase in all Cs.

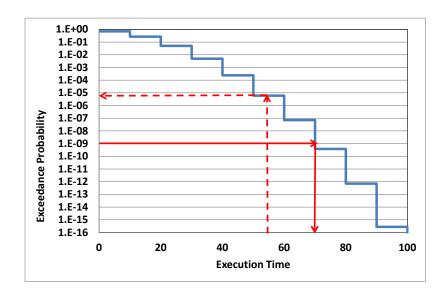

For systems executing on hardware platforms with time-randomised hardware components [115], then a probabilistic WCET (pWCET) [18, 137, 147, 164] can be obtained. The exceedance function for this probability distribution defines for any specific probability, derived from a required maximum failure rate associated with a criticality level, an execution time budget which has no greater probability of being exceeded on any given run [136]. The pWCET distribution therefore effectively defines different estimates of the WCET budget for the same task, for different criticality levels due to their different requirements on the maximum tolerable failure rate.

The focus on different computation times was extended to task periods in subsequent papers [44,48,50,58,63,97,101,472]. Here tasks are event handlers. The higher the criticality level the more events must be handled, and hence the task must execute more frequently even if it does not execute for longer.

In MCS a task is now defined by:  $(\vec{T}, D, \vec{C}, L)$ , where  $\vec{C}$  and  $\vec{T}$  are vectors of values – one per criticality level, with the constraints:

$$L1 > L2 \Rightarrow C(L1) \geq C(L2)$$

$$L1 > L2 \Rightarrow T(L1) \leq T(L2)$$

for any two criticality levels L1 and L2.

Note the completion of the model, by making D criticality dependent [58] has not as yet been addressed in detail. But it could have the constraint:

$$L1 > L2 \Rightarrow D(L1) \geq D(L2)$$

So a task may have a 'safety critical' deadline and an early Quality of Service (QoS) deadline. Alternatively:

$$L1 > L2 \Rightarrow D(L1) \leq D(L2)$$

in which case the conservative 'safety critical' deadline is shorter then the one deemed necessary if the criticality level is lower.

Another feature of many of the papers considered in this review is that the system is defined to execute in a number of criticality *modes*. A system starts in the lowest criticality mode. If all jobs behave according to this mode then the system stays in that mode. But if any job attempts to execute for a longer time, or more frequently, than is acceptable in that mode then a criticality mode change occurs. Ultimately the system may change to the highest criticality mode.

Some papers allow the criticality mode to move down as well as up, but others (indeed the majority) restrict the model to increases in criticality only. We return to this issue in Section 6.

Finally, many papers restrict themselves to just two criticality levels; high (HI) and low (LO) with HI > LO. These are referred to as *dual-criticality* systems. Where modes are used, the system is either in a LO-criticality (or normal) mode or a HI-criticality mode. And the set of task parameters is typically:  $(T_i, D_i, C_i(HI), C_i(LO), L_i)$ . At the other extreme are the models presented by Ekberg et al. [165, 167, 169] in which any number of modes are allowed and the movement between modes is represented by a directed acyclic graph.

# **3** Single Processor Analysis

Since Vestal's 2007 paper [451] there has been a series of publications. Most of these papers address single processor platforms and independent components.

#### 3.1 Job scheduling

Initially a number of papers considered the restricted problem of scheduling, on a single processor, a finite set of mixed criticality jobs with criticality dependent execution times [43,51,53,67,69,74,79,210,306,307,369,408,416,417,421]. This work has, however, largely been superseded by work on the more widely applicable task model.

### 3.2 Fixed Priority Scheduling

In this section we look at MCS schemes that are based on applying Response-Time Analysis (RTA), then those that consider slack scheduling and finally approaches that are derived from period transformations.

#### 3.2.1 RTA-Based approaches

Vestal's approach was formalised (i.e. proof that the use of Audsley's priority assignment algorithm [26] was optimal) by Dorin et al. [156] in 2010. They also extended the model to include release jitter, and showed how sensitivity analysis could be applied.

Vestal's approach allowed the priorities of high and low criticality tasks to be interleaved, but all tasks had to be evaluated as if they were of the highest criticality. By introducing monitoring of task execution time, and the prevention of execution time over-runs, higher resource usage can be delivered [58]. This is a crucial issue in mixed criticality scheduling; by the introduction of more trusted components a high utilisation of the available resources is facilitated.

In 2011 this approach was further extended [61,97] to give a scheduling model and associated analysis framework for a single processor system that dominates all previous published analysis for MCS (using fixed priority scheduling) in that it made better use of the processor and could schedule all systems that could be guaranteed by other approaches, plus many that could not. These papers were however restricted to just two criticality levels (or modes). The system's run-time behaviour is either *low-criticality* (which relies on all execution times being bound by the low-criticality values and guarantees that all deadlines are met) or *high-criticality* (where only high criticality work is guaranteed but the rely condition<sup>17</sup> is weakened – the bound on high-criticality execution times is increased). The system's criticality change (from Low to High, i.e. *LO* to *HI*) is triggered by the observation, at run-time, that the stronger rely condition has been violated. In the context of control applications Cheng et al [120] also allow the state of the controlled plant to trigger a criticality mode change.

This change in criticality level has a number of similarities to systems that move between different operational modes (although there are also some significant differences [95, 204]). In the HI-criticality mode there are fewer tasks, but they have longer execution times or shorter periods. The literature on mode change protocols [37, 108, 170, 375, 390, 412, 442, 443], however, highlights one important problem: a system can be schedulable in every mode, but not schedulable during a mode change [443]. This is also true for systems that change criticality levels.

<sup>&</sup>lt;sup>17</sup>A rely condition formalises the assumptions required for the guarantees to be valid [268].

An optimal priority ordering is defined in the paper from Baruah et al. [61] in that it maximises the priority of high criticality tasks, subject to the system being schedulable. Both the high and low criticality tasks are ordered via deadline (deadline monotonic) and a simplified version of Audsley's algorithm is used to assign priorities from the lowest to the highest level. At each priority level the lowest priority task from the low criticality task set is tried first, if it is schedulable then the algorithm moves up to the next priority level; if it is not schedulable then the lowest priority task from the high criticality set is tested. If it is schedulable then again the algorithm moves on to the next level. But if neither of these two tasks are schedulable then the search can be abandoned as the task set is unschedulable. In total a maximum of 2N tests are needed (where N is the number of tasks in the system)<sup>18</sup>. Note that this result follows from work on robust priority assignment [145]. As each set of LO/HI criticality tasks can be viewed as additional interference on the other subset, an optimal priority ordering can be obtained with each subset in Deadline Monotonic priority order and a merge operation between them.

The protocol (dropping all LO-criticality work if any task executes for more than its C(LO) value<sup>19</sup>), the derived analysis and the use of optimal priority ordering is shown [61] to out-perform other schemes (in terms of success ratio for randomly generated task sets). The analysis is based on standard RTA (Response-Time Analysis). For any task,  $\tau_i$ , first its LO-criticality response-time (R(LO)) is computed using LO-criticality parameters for all the tasks. A criticality switch must occur before this value if the task is to be impacted by the change, otherwise it will have completed execution. The worst-case response-time in the HI-criticality mode (R(HI)) is computed by noting that all LO-criticality tasks must be abandoned by time R(LO). The paper contains two methods for computing  $R(HI)^{20}$ , one involves a single upper bound, the other looks at all the possible critically change points before R(LO) and computes the worst-case. The latter is more accurate, though still not exact; however, the gain in performance is not significant and the simple upper bound test is probably sufficient in most cases.

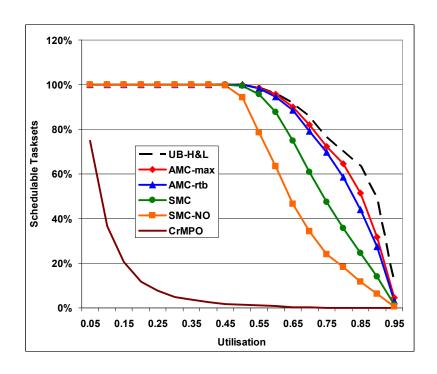

To illustrate the above approaches one of the graphs from [61] is reproduced in Figure 1. This figure plots the percentage of task sets generated that were deemed schedulable for a system of 20 tasks, with on average 50% of those tasks having high criticality and each task having a high criticality execution time that is twice its low criticality execution time. The compared approaches are (from least effective to most effective): CrMPO which assigned priorities in criticality order, SMC-NO

<sup>&</sup>lt;sup>18</sup>Strictly, only 2N-1 tests are needed as the highest priority task must be schedulable as its computation time is less than its deadline.

<sup>&</sup>lt;sup>19</sup>First proposed by Baruah [43,51].

<sup>&</sup>lt;sup>20</sup>In [61] the example in Section IV.B (final step) should have a worst-case response-time of 90, not 85 as reported in the paper; however 90 is still below the deadline of 100.

Figure 1: Percentage of Schedulable Task Sets

(static mixed criticality with no run-time monitoring) which is Vestal's original approach, SMC which is an adaptation of Vestal's approach in which LO-criticality tasks are monitored at run-time and are prevented from executing for more than C(LO), and AMC-rtb and AMC-max which are the two methods introduced in the previous paragraph (AMC for adaptive mixed criticality). In the graph the UB-H&L line bounds the maximum possible number of schedulable task sets. It serves to illustrate the quality of the AMC-max approach. Almost all publications on MCS assume that the task deadlines are constrained ( $D \le T$ ). For AMC, Burns and David [104] removed this constraint and a version of the analysis for AMC now allows arbitrary deadlines.

The AMC-rtb approach was extended by Zhao et al [475,476,479] in 2013 to incorporate preemption thresholds [398] into the model. They demonstrated a reduction in stack usage and improved performance for some parameter ranges. Another approach to combining AMC-rtb and existing scheduling theory is taken by Burns and Davis [102]. They consider the use of deferred preemption [93,142] and demonstrate a significant improvement over fully preemptive AMC-rtb. The gain in schedulability they demonstrate is obtained by having a final non-preemptive region (FNPR) at the end of C(LO) and C(HI), and by combining the assignment of

priority and the determination of the size of these FNPRs. Where scheduling analysis is part of a design optimisation Zhao and Zeng [480] argue that even AMC-rtb is too complex. They propose a new simpler test that is still safe and has bounded pessimism. At the other extreme, Asyaban and Kargahi [23] develop exact analysis for AMC, unfortunately at the cost of loosing optimal priority ordering.

In keeping with a number of papers on MCS, the work of Baruah et al. [61] (and most of the subsequent modifications) restricted itself to dual criticality systems. Fleming and Burns [182] extended these models to an arbitrary number of criticality levels, focusing particularly on five levels as this is the maximum found in automotive and avionics standards. They observed that AMC-rtb remains a good approximation to AMC-max, and that AMC-max became computational expensive for increased numbers of criticality levels. They concluded that AMC-rtb represented an adequate and effective form of analysis. A relatively minor improvement to AMC-max was published by Huang et al. [246] (they termed it AMC-IA); however there are cases where their analysis is optimistic (i.e. unsound) [186].

One characteristic of all the schemes defined above is that tasks do not change their priority after a criticality mode change. If priorities can change then a simple form of sufficient analysis is possible [62]. This work defines a new approach, PMC (priority may change). Evaluations show that PMC performs similarly to AMC-rtb, though neither dominates the other. An improved scheme, GFP (Generalised Fixed Priority) is proposed by Chen et al. [119]. They assign (using an heuristic) three priorities to each task. One for each of the two criticality levels, and one for the transition between the criticality modes. They demonstrate an improvement over AMC-rtb.

It was noted in the section on Mixed Criticality Models that the period parameter (T) can be criticality dependent as well as the worst-case execution time estimate (C). An application may consist of event handlers, and have different levels of constraint over the arrival patterns of the events. The higher the criticality, the closer together the events are assumed to arrive; and hence the smaller the T parameter. Baruah and Chattopadhyay [63] have reformulated the SMC and AMC analysis (introduced above) to apply to this model, in which the Ts rather than the Cs vary with criticality. Their evaluation results show similar behaviour to that depicted in Figure 1. Criticality specific periods are also address by Burns and Davis [101], Baruah [50], and by Zhang et al. [472] (who derived an improved analysis that they termed SAMC – Sufficient AMC).

For periodic task sets with offsets, Asyaban et al. [24] has produced feasibility analysis showing that simulation over an interval of length four times the hyperperiod plus the largest offset forms a sufficient test of schedulability.

#### 3.2.2 Slack scheduling

An alternative approach to scheduling mixed criticality fixed priority systems is, for dual-criticality systems, to use a *slack scheduling* scheme in which low criticality jobs are run in the slack generated by high criticality jobs only using their low criticality execution budgets. This was first explored by Niz et al. [356]. One difficulty with this approach is to incorporate sporadic tasks. At what point can the 'slack' of a non-appearing sporadic task be allocated to low criticality jobs? Even for periodic tasks, ensuring schedulability of high criticality tasks in all circumstances is not straightforward. Niz et al. [356] compute the time at which a high criticality task must be released to ensure that it meets its deadline (a scheme similar to the dual-priority approach outlined in Section 5.1). However, Huang et al. [245] demonstrated that if a low criticality (high priority) task executes beyond its deadline, a high criticality (lower priority) task could miss its deadline. They show that either the low criticality task must be aborted at its deadline or (more practically) its priority must be reduced to a background level. They then derive safe analysis. Niz et al. subsequently modified the enforcement rule in their model to remove the problem and improved its performance [357, 358].

While slack is usually generated by tasks not executing for their full budget, it is also produced by the arrival of jobs being less frequent than anticipated in the worst-case. Neukirchner et al. [351, 352] adapt and extend a number of schemes for monitoring activation patterns. Their multi-mode approach is proved to be safe (no false negatives) and efficient (few false positives). Hu et al. [244] also consider budget management, and produce an effective scheme for minimising the overheads associated with slack management.

For a dual-criticality system C(LO) values must, of course, be known. Once schedulability has been established however, it is possible to derive [404], using sensitivity analysis [84, 383], a scaling factor F (F>1) such that the system remains schedulable with all C(LO) values replaced by  $F \cdot C(LO)$ . Using these scaled values at run-time will increase the robustness of the system, as the LO-criticality tasks will be able to execute for a greater time before a criticality change is triggered. Scaling can also be applied to the C(HI) values. Volp et al. [456] look at an alternative means of obtaining C(LO) and C(HI) values; they do not consider them to be estimates of worst-case execution time, but budgets set by some design optimisation process.

As scaling involves changing a task's computation time, and computation time influences priority assignment, it is possible to extend this approach by also allowing priorities to change as the system is made more robust [98]. A more dynamic budget management scheme is used by Gu and Easwaran [212] to postpone criticality level mode changes within the context of the EDF-VD scheme (see Section 3.3).

Sciandra et al. [407] are extending and applying scaling factors to intelligent transport systems. Issues of robustness are also addressed by Herman et al. [235].

#### 3.2.3 Period transformation

As Vestal noted [451], an older protocol period transformation [410,411] (PT), is also applicable to the mixed criticality scheduling problem. Period transformation splits a task with period T and computation time C into two (or more) parts so that the task now has the parameters T/2 and C/2. Assuming all tasks have deadlines equal to their periods, the application of the optimal rate monotonic priority assignment scheme [319] will increase the relative priority of all transformed tasks. If all high criticality tasks are transformed so that their transformed periods are shorter than all low criticality tasks then the rate monotonic algorithm will deliver partitioned (i.e. criticality monotonic) priorities. All high criticality tasks will have priorities greater than all lower criticality tasks. The scheme can easily be extended to task sets with constrained deadlines (D < T). However, the scheme does introduce extra overheads from the increased number of context switches, and these could be excessive if there are low criticality tasks with short deadlines. A simple example of a period transformed task would be one with T = D = 16, C(HI) = 8and C(LO)=4; this task could be transformed to one with T=D=4 and C=2Note, this is C(HI)/4, not C(LO)/4). The computation time is such that if the task executes according to its HI-criticality parameter it will take four invocations of the transformed task to complete, but if the LO-criticality assumption is valid it will only take two.

If overheads are ignored then Period Transformation performs well. Baruah and Burns postulate [59] (and prove for two tasks) that this is primarily due to the inherent property of PT to deliver tasks sets with harmonic periods (that are then more likely to be schedulable). It does not seem that PT is of specific benefit to MCS.

To split the code of a task, either a static code transformation process must be used or the run-time must employ an execution-time server. With code transformation, the programmer must identify where in the code the split should be made. This does not lead to good code modularisation and is similar to the problems encountered when functions must to be split into short sections so that they can be 'packed' into the minor cycles of a cyclic executive [109]. There is also the problem of OS locks being retained between slices of the code; making the protected resource unavailable to other tasks.

With a dual-criticality task such as the one in the example above the point at which the task can be assumed to have executed for two units of time is itself criticality dependent. This to all intents and purposes makes code transformation im-

practical. Therefore, if the code is not to be changed then a run-time server must be used to restrict the amount of computation allowed per release of the (transformed) task. In practice this means that:

- Without PT, LO-criticality tasks may have high priorities and hence their execution times must be monitored (and enforced); HI-criticality tasks must also be monitored as they may need to trigger a criticality change if they execute for more than C(LO) thereby triggering the abandonment of LO-criticality tasks.

- With PT, LO-criticality tasks have the lower priorities and hence they do not need to be monitored, HI-criticality tasks must be monitored to enforce the per release budget.

In general, there is less run-time intervention with PT. But recall there is considerably more task switching overhead if the periods of all HI-criticality tasks are reduced to less than all LO-criticality task periods.

For multiple criticality levels a number of transformations may be required to generate a criticality monotonic ordering [182]. For example if there are three tasks (H, M, and L) with criticality levels implied by their names, and periods 5, 33 and 9. Then first M must be divided by 11 to get a period of 3 (so less than 9), but then H must be divided by 5 to move it below the new value for M. As a result the transformed periods become 1, 3 and 9. It also seems that the theoretical benefit of PT diminishes with an increased number of criticality levels [182].

#### 3.3 EDF Scheduling

The first paper to consider MCS with EDF scheduling was Baruah and Vestal [75] in 2008. Park and Kim [369] later introduced a slack-based mixed criticality scheme for EDF scheduled jobs which they called CBEDF (Criticality Based EDF). In essence they use a combination of off- and on-line analysis to run HI-criticality jobs as late as possible, and LO-criticality jobs in the generated slack. In effect they are utilising an older protocol developed by Chetto and Chetto [121] for running soft real-time tasks in the 'gaps' produced by running hard real-time tasks so as to just meet their deadlines.

A more complete analysis for EDF scheduled systems was presented by Ekberg and Yi [166,216]. They mimicked the FP scheme by assigning two relative deadlines to each high criticality task. One deadline is the defining 'real' deadline of the task, the other is an artificial earlier deadline that is used to increase the likelihood of high criticality tasks executing before low criticality ones. At the point that the criticality of the system changes from low to high (due to a task exceeding its low

criticality budget), all low criticality tasks are abandoned and the high criticality tasks revert to their defining deadlines. They demonstrate a clear improvement over previous schemes [217]. Later work [167] generalises the model to include changes to all task parameters and to incorporate more than two criticality levels. Tighter analysis is provided by Easwaran [161], although it is not clear that the method will scale to more than two criticality levels. Further improvements are presented by Yao et al. [465]. They use an improved schedulability test for EDF (a scheme called QPA [471]), and a genetic algorithm (GA) to find better artificial deadlines.

A similar scheme was presented by Baruah et al. [54,56], called EDF-VD (EDF - with virtual deadlines). Again for a dual-criticality system, HI-criticality tasks have their deadlines reduced (if necessary) during LO-criticality mode execution. All deadlines are reduced by the same factor. They demonstrate both theoretically and via evaluations that this is an effective scheme. Note, however, that this scheme is not as general as those reported above [161,166,216]. In these approaches a different reduction factor is used for each task. Nevertheless the use of a single value does allow schedulability bounds to be derived (see Section 7). An intermediate approach that uses just two scaling factors is provided by Masrur et al. [330]; there motivation being to develop an efficient scheme that could be used at run-time. In later work [76] Baruah has generalised the underlying MCS model to include criticality-specific values for period and deadline as well as WCET. EDF-VD was further improved by Gu and Easwaran [213] by the development of a new scheduling test.

EDF scheduling of MCS is also addressed by Lipari and Buttazzo [318] using a reservation-based approach. Here sufficient budget is reserved for the high criticality tasks, but if they only make use of what is assumed by their low criticality requirements then a set of low criticality tasks can be guaranteed. Again only two criticality levels are assumed. In effect low criticality tasks run in capacity reclaimed from high criticality tasks. Deadlines for the high criticality tasks are chosen to maximise the amount of capacity reclaiming.

A different approach to using spare capacity was derived by Su at al. [429,430] by exploiting the *elastic task model* [111] in which the period of a task can change. They propose a minimum level of service for each LO-criticality task  $\tau_i$  that is defined by a maximum period,  $T_i^{max}$ . The complete system must be schedulable when all HI-criticality tasks use their C(HI) values and all LO-criticality tasks use their C(LO) and  $T^{max}$  values. At run-time if HI-criticality tasks use less than their full HI-criticality entitlement then the LO-criticality tasks can run more frequently. They demonstrate that for certain parameter sets their approach performs better than EDF-VD.

Alternative analysis for EDF scheduled MCS is presented by Santinelli et al. [400].

Their use of multiple demand-bound curves allows sensitivity analysis to be derived that can be applied to the trade-off between resource usage and schedulability (within the context of MCS).

#### 3.4 Shared Resources

With mixed criticality systems it is not clear to what extent data should flow between criticality levels. There are strong objections to data flowing from low to high criticality applications unless the high criticality component is able to deal with potentially unreliable data [409] – this happens with some security protocols [83]. Even with data flowing in the other direction there remains the scheduling problem of not allowing a high criticality task to be delayed by a low criticality task that has either locked a shared resource for longer than expected or is executing at a raised priority ceiling level for too long.

Sharing resources within a criticality level is however a necessary part of any usable tasking model. In single criticality systems a number of priority ceiling protocols have been developed [39,413]. These are beginning to be assessed in terms of their effectiveness for mixed criticality systems. Burns [94] extends the analysis for fixed priority systems by adding criticality specific blocking terms into the response-time analysis. He notes that the original form of the priority ceiling protocol (OPCP) [413] has some useful properties when applied to MCS. Resources can be easily partitioned between criticality levels and starvation of *LO*-criticality tasks while holding a lock on a resource can be prevented. With AMC-OPCP, a task can only suffer direct blocking if a resource is locked by a lower priority task of the same criticality.

Rather than use a software protocol, Engel [171] employs Hardware Transactional Memory to roll back any shared object to a previous state if a *LO*-criticality task overruns its budget while accessing the object.

For EDF-based scheduling Zhao et al. [475,478] attempt to integrate the Stack Resource Protocol (SRP) [39] and Preemption Threshold Scheduling [460] with approaches to EDF scheduling that involve tasks having more than one deadline. This is not straightforward as these schemes assume that relative deadlines are fixed.

Alternative approaches are proposed by Lakshmanan et al. [292] by extending their single processor zero slack scheduling approach [356] to accommodate task synchronisation across criticality levels for fixed priority systems. They define two protocols: PCIP (Priority and Criticality Inheritance Protocol) and PCCP (Priority and Criticality Ceiling Protocol). Both of these contain the notion of criticality inheritance. This notion is also used by Zhao et al. [477] in their HLC-PCP (Highest-Locker Criticality Priority Ceiling Protocol) which they apply to the

AMC scheduling scheme (see Section 3.2.1). For a dual criticality system they define three modes of execution, the usual two plus an intermediate mode which covers the time during which LO-criticality tasks are allowed to continue to execute if they are holding a lock on a resource that is shared with a HI-criticality task.

A more systematic scheme is proposed by Brandenburg [90]. Here all shared resources are placed in *resource servers* and all access to these servers is via a MC-IPC protocol. As a result only these servers and the support for the MC-IPC protocol have to be developed to the highest criticality level. Resource users can be of any criticality level, including non-critical. Data sharing within the context of the  $MC^2$  architecture (see Section 4) is address by Chisholm et al. [123].

# 3.5 Static and Synchronous Scheduling

The move between criticality levels can be captured in a static schedule by switching between previously computed schedules; one per criticality level. This is explored by Baruah and Fohler [68]. Socci et al. [419, 421, 422] show how these Time-Triggered (TT) tables can be produced via first simulating the behaviour one would obtain from the equivalent fixed priority task execution. Their approach is improved upon by Behera and Bhaduri [79] (their algorithm has lower computational complexity). Construction of the tables via tree search is addressed by Theis et al [437], and via the use of linear programming (LP) by Jan et al. [264]. For legacy systems Theis and Fohler [436] show how an existing single table may be used to support MCS.

A particularly simple table driven approach is to use a cyclic executive, this is investigated by Burns et al. [60, 99, 106, 151, 181, 184, 185] for multiprocessor systems in which the change from minor cycle to minor cycle is synchronised as is the change from executing code of one criticality to that of another. Both global and partitioned approaches are investigated, as are systems that use less processors for the HI-criticality work than they do for the LO-criticality work [185]. Both LP and ILP based formulations are used to construct the cyclic executives.

This use of tables is extended to synchronous reactive programs by Baruah [45, 46]. Here a DAG (Directed Acyclic Graph), of basic blocks that execute according to the synchrony assumption, is produced that implements a dual-criticality program. The synchronous approach is also considered by Yip et al. [466] and by Cohen et al. [132]. The latter proving an application of mixed criticality from the railway industry, and an example of why data needs to flow between criticality levels.

### 3.6 Varying Speed Processors

Most analysis for MCS assumes a constant speed processor, but there are situations in which the speed of the processor is not known precisely (for example with asynchronous circuitry). Baruah and Guo [70] consider power issues that could lead to a processor having variable speed. As a processor slows down the execution time of the tasks increase. They simplify the model by assuming two basic speeds, normal and degraded. At the normal speed a scheduling table is used; at the degraded speed only HI-criticality jobs are executed and they use EDF. The authors have extended this work [71,219,221] to include a more expressive model, issues of processor self-monitoring (or not), and a probabilistic approach to performance variation. They have also considered system which have both uncertainty in execution times and processor speed [222].

Voltage scheduling, and thereby variable speed computation, is used by Huang et al. [250, 251] to respond to a temporal overload – if a C(HI) value is exceeded and could lead to a LO-criticality task missing its deadline then energy is utilised to enable the processor to reduce computation times. Overall, their approach aims to reduce the system's expected energy consumption. Taherin et al. [431] present some alternative DVFS schemes and compare their results with those of Huang. DVFS management is also addressed by Haririan and Garcia-Ortiz [230] in their provision of a simulation framework for power management.

# 4 Multiprocessor Analysis

The first paper to discuss mixed criticality within the context of multiprocessor or multi-core platforms was by Anderson et al. [20] in 2009 and then extended in 2010 [342]. Five levels of criticality were identified; going from level-A (the highest) to level-E (the lowest). They envisaged an implementation scheme, which they call  $MC^2$ , that used a cyclic executive (static schedule) for level-A, partitioned preemptive EDF for level-B, global preemptive EDF for levels C and D and finally global best-effort for level-E. They considered only harmonic workloads but allowed slack to move between containers (servers). Each processor had a container for each criticality level, and a two-level hierarchical scheduler (see Section 5.4). Later work from this group [124, 235] evaluates the OS-induced overheads associated with multiprocessor platforms. They also experimented with isolation techniques for LLC (last level cache) and DRAM. And have demonstrated, using  $MC^2$ , the benefits of having different isolation techniques for each criticality level [279, 280]. The support for mode changes within  $MC^2$  is considered by Chrisholm [122]. This  $MC^2$  framework is also used by Bommert [89] to support segmented mixed criticality parallel tasks.

In the remainder of this section we first look at task allocation (with global or partitioned scheduling), then consider analysis and finally communications and other systems resources. We note that there has also been work on implementing mixed-criticality synchronous systems on multiprocessor platforms [47].

#### 4.1 Task Allocation

The issue of allocation was addressed by Lakshmanan et al. [293] by extending their single processor slack scheduling approach [356] to partitioned multiprocessor systems employing a Compress-on-Overload packing scheme. Allocation in a distributed architecture was addressed by Tamas-Selicean and Pop [432–435] in the context of static schedules (cyclic executives) and temporal partitioning. They observed that scheduling can sometimes be improved by increasing the criticality of some tasks so that single-criticality partitions become better balanced. This increase comes at a cost and so they employ search/optimisation routines (Simulated Annealing [191, 433] and Tabu [256, 257, 432, 434]) to obtain schedulability with minimum resource usage. Search routines, this time GAs (Genetic Algorithms), are also used by Zhang et al. [473] to undertake task placement in security-sensitive MCS. Their objective is to minimise energy consumption "while satisfying strict security and timing constraints". A toolset to aid partitioning is provided by Alonso et al. [17].

A more straightforward investigation of task allocation was undertaken by Kelly et al [277]. They considered partitioned homogeneous multiprocessors and compared first-fit and best-fit approaches with pre-ordering of the tasks based on either decreasing utilization or decreasing criticality. They used the original analysis of Vestal to test for schedulability on each processor, and concluded that in general first-fit decreasing criticality was best. For heterogeneous multiprocessors Awan et al. [35] propose a mapping scheme that is energy efficient.

A comprehensive evaluation of many possible schemes is reported by Rodriguez at al. [394]. They consider EDF scheduling and used the analysis framework of EDF-VD (see Section 3.3). One of their conclusions is the effectiveness of a combined criticality-aware scheme in which HI-criticality tasks are allocated Worst-Fit and LO-criticality tasks are allocated using First-Fit; both with Decreasing Density. The same result is reported by Gu et al. [209]. They additionally note that if there are some very 'heavy' LO-criticality tasks (i.e. high utilisation or density) then space must be reserved for them before the HI-criticality tasks are allocated. Partitioning with EDF-VD is also addressed by the work of Han et al. [227]. Ramanathan and Easwaran [385] demonstrate that an effective partitioning scheme can be derived from evenly distributing the differences between HI-criticality and LO-criticality utilisation. Their results being applicable to EDF-VD

and fixed-priority AMC.

A global allocation scheme for MCS is proposed by Gratia et al. [201, 203]. They adapt the RUN scheduler [392], which uses a hierarchy of servers, to accommodate HI and LO criticality tasks. The latest version of their schedular (GMC-RUN) [202] has been extended to deal with more criticality levels.

Between fully partitioned and fully global scheduling is the class of schemes termed *semi-partitioned*. This is being addressed by Bletsas at al. [32, 86, 87] and Al-Bayati et al. [8]. The latter work uses two allocations for their two criticality modes. *HI*-criticality tasks do not migrate. During a mode change, carry-over *LO*-criticality jobs are dropped and new *LO*-criticality jobs executing on a different processor are given extended deadlines/periods (i.e. they utilise the elastic task model). A different approach is taken by Xu and Burns [464]; here a mode change on one processor results in *LO*-criticality jobs migrating to a different processor that has not suffered a criticality mode change. No deadlines are missed. If all processors suffer such a mode change then at least the timing needs of all *HI*-criticality tasks are protected.

A different approach, that aims to maximise the benefits of partitioning and global scheduling, is that based on clusters. A multi-core platform is statically partitioned into a number of clusters, within a cluster tasks execute 'globally'. Ali and Kim [13] investigate a scheme in which small clusters are used when the system is in the LO-criticality mode, but larger clusters are employed when the system moves to the HI-criticality mode. Nagalakshmi and Gomathi [347] also use clusters but within a EDF-scheduled fully partitioned approach. Within each cluster is a single HI-criticality task and one or more LO-criticality tasks. As a result the impact of a HI-criticality task executing beyond its C(LO) value is limited to just those LO-criticality tasks within the same cluster.

With dual-criticality fault tolerant systems, a scheme in which high criticality tasks are replicated (duplicated) while low criticality tasks are not is investigated by Axer et al. [36] for independent periodic tasks running on a MPSoC (multiprocessor system-on-chip). They provide reliability analysis that is used to inform task allocation.

A more theoretical approach (i.e. it is not directly implementable) is proposed by Lee et al. [298] with their MC-Fluid model. A fluid task model [65, 241] executes each task at a rate proportional to its utilisation. If one ignores the cost of slicing up tasks in this way then the scheme delivers an optimal means of scheduling multiprocessor platforms. To produce a mixed criticality version of the fluid task model the fact that tasks do not have a single utilisation needs to be addressed. Lee et al. [298, 299] do this and they also produce an implementable version of the model that performs well in simulation studies (when compared with other approaches). Baruah et al. [41,66] derived a simplified fluid algorithm which they

call MCF. Two further algorithms, MC-Sort and MC-slope, are proposed by Ramanathan and Easwaran [384, 387].

All the above work is focussed on standard single threaded tasks. In addition there has been some studies on parallel tasks and MCS – see Liu et al. [309, 310, 322], Pathan [373] and Agrawal and Baruah [4].

### 4.2 Schedulability Analysis

For globally scheduled systems Li and Baruah [308] take a 'standard' multiprocessor scheme, fpEDF [42] and combine it with their EDF-VD approach (see Section 3.3). Evaluations indicate that this is an effective combination. Extensions of this work [64] compare the use of partitioning or global scheduling for MCS. Their interim conclusion is that partitioning is by far the most effective approach to adopt.

Notwithstanding this result, Pathan derives [370] analysis for globally scheduled fixed priority systems. They adopt the single processor approach [61] (see Section 3.2) and integrate this with a form of analysis for multiprocessor scheduling that is amenable to optimal priority ordering, via Audsley's algorithm [26]. They demonstrate the effectiveness of their approach (by comparing success ratios). Jung and Lee subsequently improved on this analysis [270].

A different and novel approach to multi-core scheduling of MCS is provided by Kritikakou et al. [285,288]. They identify that a HI-criticality task will suffer interference from a LO-criticality task running on a different core due to the hardware platform's use of shared buses and memory controllers etc.. They monitor the execution time of the HI-criticality task and can identify when no further interference can be tolerated. At this point they abort the LO-criticality task even though it is not directly interfering. An implementation on a multi-core platform demonstrated effective performance of their scheme [288]. They subsequently improved on this static approach by utilising a dynamic version that reduces the time spent in the controller [286].

Extensions to deal with precedence constraints were given by Socci et al. [420] but only for jobs (not tasks). A full pipeline scheme is considered by de Niz et al. [150].

#### 4.3 Communication and other Resources

With a more complete platform such as a multiprocessor or System on Chip (SoC), perhaps with a NoC (Network-on-Chip), more resources have to be shared between criticality levels. The first design issue is therefore one of partitioning (as addressed above), how to ensure the behaviour of low criticality components does not adversely impact on the behaviour of higher criticality components. Pellizzoni

et al. [376] in 2009 was the first to consider the deployment of mixed criticality systems (MCS) on multi-core and many-core platforms. They defined an Architectural Analysis and Design Language (AADL), a form of ADL (Architectural Description Language), for mixed criticality applications that facilitates system monitoring and budget enforcement of all computation and communication. Later Obermaisser et al. [363, 364] introduce a system model with gateways and end-to-end channels over hierarchical, heterogeneous and mixed criticality networks.

For a bus-based architecture it is necessary to control access to the bus so that applications on one core do not impact unreasonably on applications on other cores (whether of different or indeed the same criticality level). Pellizzoni et al. [377] show that a task can suffer a 300% increase in its worst-case execution time due to memory access interference even when it only spends 10% of its time on fetching from external memory on an 8-core system. To counter this, Yun et al. [467] propose a memory throttling scheme for MCS. Kotaba et al [284] also propose a monitoring and control protocol to prevent processes flooding any shared communication media be it a bus or network. Kritikakou et al. [287] consider a scenario in which there are a few critical tasks that can suffer indirect interference from many lower critical tasks. They attempt to allow as much parallelism as possible commensurate with the critical tasks retaining their temporal validity. Hassan and Patel [231] claim an improved bus arbitrator, called Carb, that is more criticality aware. Bounding the interference that a safety-critical task can suffer from lower criticality tasks using the same shared communication resources on a multi-core platform is also addressed by Nowotsch et al. [361]. Freitag et al. [187] utilise a fully isolated model (each core only has tasks of only one criticality), those core that have LO-criticality tasks are slowed down (or even stopped) if their measured interference on the HI-criticality cores is above statically derived bounds.

Within the time-triggered model of distributed computation and communication a mixed criticality system is often viewed as one that has both time-triggered and event-triggered activities, also referred to as synchronous and asynchronous [382, 425]. The time-triggered traffic is deemed to have the highest criticality, the event-triggered traffic can be either just best-effort or can have some level of assurance if its impact on the system is bounded; what Steiner [425] calls *rate-constrained*. Protocols that support this distinction can be supported on networks such as TTEthernet. Another TDMA-based approach, though this time built into the Real-Time Ethernet protocol, is proposed by Carvajal and Fischmeister in their open-source framework, *Atacama* [114]. Cilku at al. [128] describe a TDMA-based bus arbitration scheme. Novalk et al. [359] propose a scheduling algorithm for time-triggered traffic that minimises jitter while allowing *HI*-criticality messages to be re-transmitted (following failure) at the expense of *LO*-criticality messages (which are abandoned). They also [360] consider how to produce an effective

static schedule when there are unforeseen re-transmissions (for two and three levels of criticality). Analysis of AFDX (Avionics Full Duplex Switched Ethernet) within the context of MCS is provided by Finzi et al. [180].

A reconfigurable SDRAM controller is proposed by Goossen et al. [199] to schedule concurrent memory requests to the same physical memory. They also use a TDMA approach to share the controller's bandwidth. A key aspect of this controller is that it can adapt to changes in the run-time characteristics of the application(s). For example, a criticality mode change which should result in more bandwidth being assigned to the higher criticality tasks can be accommodated by what the authors call a *use-case switch*. Criticality aware DRAMs are also addressed by Jalle et al [263] in the context of a Space case study in which there are two criticality levels: 'control' and 'payload'.

Virtual DRAMs are adapted by Ecco et al. [163] to isolate critical tasks (which are guaranteed) from non-critical tasks that, although not guaranteed, do perform adequately. Each virtual device represents a group of DRAM banks supports one critical task and any number of non-critical tasks. All critical tasks run on dedicated cores, and hence the only potential source of inter-criticality interference is from the interconnection fabric (bus). By use of virtual devices, the critical tasks benefit from interference-free memory access. DRAMs are also the focus of the work by Hassen et al [232], Awan et al [31] and Guo and Pellizzon [218].

Kim at al. [278] propose a priority-based DRAM controller for MCS that separates critical and non-critical memory accesses. They demonstrate improved performance for the non-critical traffic. Note this work is focussed on supporting critical and non-critical traffic on the same memory banks (rather than mixed-criticality). A similar approach and result is provided by Goossens et al. [198] with their open-page policy.

Giannopoulou et al. [191, 192] use a different time-triggered approach. They partition access to the multiprocessor bus so that at any time, t, only memory accesses from tasks of the same criticality can occur. This may introduce some inefficiencies, but it reduces the temporal modelling of a mixed criticality shared bus to that of a single criticality shared bus. The latter problem is not, however, straightforward (but is beyond the scope of this review). In later work they generalise their approach by introducing the notion of isolation scheduling [247]. They also demonstrate the implementation of their approach on a Layray MPPA-256 many-core platform [446].

The problems involved in using a shared bus has lead Giannopoulou et al. to also include a Network-on-Chip (NoC) in their later work [194]. Burns et al. [60, 99, 106, 184] apply a 'one criticality at a time' approach to MCS scheduled by the use of a Cyclic Executive; they considered both partitioned and global allocation of jobs to frames.

Tobuschat et al. [444, 445] have developed a NoC explicitly to support MCS. Their IDAMC protocol uses a *back suction* technique [153] to maximise the bandwidth given to low (or non) critical messages while ensuring that high-criticality messages arrive by their deadlines. The more familiar wormhole routing [355] scheme for a NoC has been expanded by Burns, Harbin and Indrusiak [107, 258] to provide support for mixed criticality traffic. Response-time analysis, already available for such protocols  $[414]^{21}$ , is augmented to allow the size and frequency of traffic to be criticality aware. Wormhole routing is also used by Hollstein et al [240] to provide complete separation of mixed-criticality code; they also support run-time adaptability following any fault identified by a Built-In Self Test. Another wormhole router (DAS - double arbiter and switching) is described by Dridi et al. [158, 159]; they use wormhole for the LO-criticality traffic, but storeand-forward for the HI-criticality messages.

On-chip networks require reliable/trusted interfaces to prevent babbling behaviour [92]; Ahmadian and Obermaisser [6] describe how to provide this via a time-triggered extension layer for a mixed-criticality NoC. Dynamic and adaptive control of a mixed-criticality NoC is considered by Kostrzewa et al. [282, 283]. Control over I/O contention via an Ethernet-based criticality-aware NoC is advocated by Abdallah et al. [1]. A focus on NoC secuity, in which HI-criticality messages need more protection than LO-criticality is taken by Papastefanakis et al. [368].

An alternative to using a NoC for all traffic (task to task and task to off chip memory) is proposed by Audsley [27, 196]. They advocate the use of a separate memory hierarchy to link each core to off chip memory. A criticality aware protocol is used to pass requests and data through a number of efficient multiplexers. If the volume of requests and data is criticality dependent then analysis similar to that used for processor scheduling can be used on this memory traffic. The separation of execution-time from memory-access time is explored by Li et al. [312,313]. They demonstrate that this distinction improves schedulability.

Controller Area Network (CAN) [195] is a widely used network for real-time applications, particularly in the automotive domain. It has been the subject of considerable attention with Response-Time Analysis derived [146] for what is, in essence, a fixed priority non-preemptive protocol. The use of CAN in mixed criticality applications has been addressed by Burns and Davis [101]. In this work it is the period of the traffic flows and the fault model that changes between criticality levels. A MixedCAN protocol was developed that makes use of a Trusted Network Component that polices the traffic that nodes are allowed to send over the

<sup>&</sup>lt;sup>21</sup>This analysis has been show to be optimistic in some circumstances, see discussion by Xiong et al. [463].

network. Evaluations are used to show the advantages of using MixedCAN rather than a criticality agnostic approach. However the paper, in keeping with many other publications, only considered dual-criticality systems.

Herber et al. [234] also addressed the CAN protocol. They replaced the physical network controller with a set of virtual controllers that facilitate spacial separation. A weighted round robin scheduler in then used to give temporal isolation. Their motivation is to support virtualisation in an automotive platform. They do not however use criticality specific parameters for the different applications hosted on the same device. Nager et al. [348] show how CAN can be used in a more flexible way to support MCS.

Other protocols that have been considered in terms of their support for mixed criticality systems include FlexRay [200] and switched Ethernet [134, 135]. In the latter work, a change in criticality mode is broadcast to the entire system by adding a new field to the IEEE 1588 PTP (Precision Time Protocol). George et al. [188] assume the speed of the wireless communication media varies over time. Each node monitors this speed and only send messages that are compatible with its current estimate. Offline analysis partitions the messages according to criticality and required speed.

A further communication protocol is addressed by Addisu et al. [3]. They consider JPEG2000 Video streaming over a wireless sensor network. With such a network the available bandwidth varies in an unpredictable way. They propose a bandwidth allocation scheme that is criticality aware. A wireless protocol (WirelessHART) is also used by Jin at al. [266, 267] to support delay analysis with fixed priority scheduling for sensor networks. A hybrid scheduling approach for sensor nodes with mixed-criticality tasks is investigated by Micea et al. [339].

A means of modelling an entire end-to-end vehicular embedded system including various forms of networking is provided by Mubeen et al. [344].

A novel scheduling approach (triangle scheduling) for mixed-criticality messages is proposed by Dürr et al. [160]. The adaptation of synchronisation protocols such as MSRP (Multiprocessor Stack Resource Policy) to multiprocessor platforms and mixed-criticality software scheduled using partitioned EDF is addressed by Han et al. [226].

# 5 Links to other Research Topics

#### 5.1 Hard and Soft Tasks

Although the label 'Mixed Criticality Systems' is relatively new, many older results and approaches can be reused and reinterpreted under this umbrella term. In particular dual-criticality systems in which there are hard and soft tasks combined

has been studied since at least 1987 [302]. Hard tasks must be guaranteed. Soft tasks are then given the best possible service. But soft tasks are usually unbounded in some sense (either in terms of their execution time or their arrival frequency) and hence they must be constrained to execute only from within *servers* (execution-time servers). Servers have bounded impact on the hard tasks. Since 1987 a number of servers have been proposed. The major ones for fixed priority systems being the Periodic Server, the Deferrable Server, the Priority Exchange Server (all described by Lehoczky et al. [302]), and the Sporadic Server [423]. The ability to run soft tasks in the slack provided by the hard tasks is also supported by the Slack Stealing schemes [139, 148, 301, 389] which have similar properties to servers. These all have equivalent protocols for dynamic priority (EDF) systems; and some EDF specific ones exist such as the Constant Bandwidth server [316].

Since their initial specification, analysis has improved and means of allocating and sharing capacity between servers have been investigated (see for example [80,81,468]). However, these results on servers (and examples of how they can be implemented in Operating Systems and programming languages) are generally known (see standard textbooks [109, 112, 323]), hence they are not reviewed in more detail here. Note however, that standard servers only deal with the isolation/partitioning aspect of MCS. To support sharing (of resources) there must be some means of moving capacity from the under utilised servers of high criticality tasks to the under provisioned servers of lower criticality tasks. The Extended Priority Exchange server [423] as well as work on making use of gain time, show how this can be achieved.

Another way of maximising the slack available for soft tasks is the dual-priority scheme [110, 149]. Here there are three bands of priority. The soft tasks run in the middle band while the hard tasks start in the lower band but are promoted to the higher band at the latest possible time commensurate with meeting their deadlines. So hard tasks execute when they have to, or when there are no soft tasks, soft tasks run otherwise.

Run-time adaptability for MCS has been addressed by Hu et al. [242, 243]. They present an approach to adaptively shape at runtime the inflow workload of LO-criticality tasks based on the actual demand of HI-criticality tasks. This improves the QoS of LO-criticality tasks; but it not clear what level of guarantee is provided for these tasks. An alternative scheme, with the same aim, is given by Hikmet [238]. A QoS focus is also taken by Vaidhun et al. [449] with respect to pervasive systems.

### **5.2** Fault Tolerant Systems (FTS)

Fault tolerant systems typically have means of identifying a fault and then recovering before there is a system failure. Various recovery techniques have been proposed including exception handling, recovery blocks, check-points, task reexecution and task replication. If, following a fault, extra work has to be undertaken then it follows that some existing work will need to be abandoned, or at least postponed. And this work must be less important than the tasks that are being re-executed. It follows that many fault tolerant systems are, in effect, mixed criticality.

To identify a fault, timeouts are often used. A job not completing before a deadline is evidence of some internal problem. Earlier warning can come from noting that a job is executing for more than its assumed worst-case execution time. Execution-time monitoring is therefore common in safety critical systems that are required to have at least some level of fault tolerance. Again this points to common techniques being required in FTS and MCS.

As noted earlier, in the discussion on CAN (Section 4.3), a fault model can be criticality dependent [101] – a task may, for example, be required to survive one fault if it is mission critical, but two faults if it is safety critical. The difference between the assumed computation times at different criticality levels may be a result of the inclusion or not of recovery techniques in the assumed worst-case execution time of tasks.

Although there is this clear link between FTS and MCS there has not yet been much work published that directly addresses fault-tolerant mixed criticality systems. Exceptions being work by Huang et al. [253, 254], a paper by Pathan [371] that focuses on service adaptation and the scheduling of fault-tolerant MCS, and a four-mode lockstep model developed by Al-Bayati et al. [7] (the requirement for lockstep execution is relaxed in later work [113]). Work by Thekkilakattil uses Zonal Hazard Analysis and Fault Hazard Analysis [439] and Error-Burst models [438] to deliver both flexibility and real-time guarantees for the most critical tasks. Thekkilakattil et al. [440] also considers the link between MCS and the tolerance of permanent faults. Lin et al. [314] attempt to integrate mixed criticality with the use of primary and backup executions in both of the two criticality modes they consider. Islam at al. [259], in a paper that preceded that of Vestal, looked at combining different levels of replication for different levels of criticality. Co-scheduling loosely-coupled replicas for MCS is shown to be effected by Rambo and Ernst [388]. Ahmadian et al. [5] invoke reconfiguration to provide for fault tolerance in the context of a time-triggered NoC based MCS. Alahmad and Gopalakrishnan [10] use what they term 'isochronous' execution to synchronise the execution of redundant versions of critical software over 'regular' and 'safe' processors.

As highlighted already in this review, many models and protocols for mixed criticality behaviour allow the system to move through a sequence of criticality modes. With a two mode system (HI and LO) the system starts in the LO mode in which all deadlines of all tasks are guaranteed, but can then transition to the HI mode in which only the HI-criticality tasks are guaranteed (and the LO-criticality tasks may actually be abandoned). It may, or may not, later return to the LO mode when it is safe to do so. Burns [95] attempts to compare these criticality mode changes with the more familiar system mode change. He concludes that the LO mode behaviour should be considered to be the 'normal' expected behaviour. A move away from this mode is best classified as a fault; with all other modes being considered forms of graceful degradation. Such a mode change is planned but may never occur. A move back to the fully functional LO mode is closest in nature to an operational (sometime known as exceptional) mode change.

### 5.3 Security

Many MCS papers have, either explicitly or implicitly, focused on issues of safety and reliability. Criticality can however also refer to security. Within this domain it is usual to have different security levels. And hence much of the extensive literature on security is relevant, but is out of scope of this review. Some work is nevertheless applicable to safety and security; for example the definition of a *separation kernel* for a system-on-chip built using a time-triggered architecture [461]. An overview of the security (and other) issues associated with MPSoCs is provided by Hassan [233].

Another paper directly linking security and MCS is from Baek and Lee [38]. They incorporate the cost of flushing between security levels in a non-preemptive version of AMC (for fixed priority scheduling).

### 5.4 Hierarchical Scheduling

One means of implementing a MCS where strong partitioning is needed between applications is to use a hierarchical (typically two-level) scheduler. A trusted base scheduler assigns budgets to each application. Within each application a secondary scheduler manages the threads of the application. There are a number of relevant results for such resource containment schemes (e.g. [117, 143, 144, 317, 396, 470]). Both single processor and multiprocessor platforms can support hierarchical scheduling.

Unfortunately when hierarchical scheduling is applied to MCS there is a loss of performance [291]. A simple interface providing a single budget and replenishment period (which is often associated with virtualisation or the use of a hypervi-

sor [16]) is too inflexible to cater for a system that needs to switch between criticality levels. To provide a more efficient scheme, Lackorznshi et al. [291] propose 'flattening' the hierarchy by exposing some of the interval structure of the scheduled applications. They develop the notion of a scheduling context which they apply to MCS [455]. In effect they assign more than one budget to each 'guest' OS. As a result, applications that would otherwise not be schedulable are shown to utilise criticality to meet all deadlines. An alternative, but still flexible approach, is provided by Groesbrink et al. [206, 207]. They allow budgets to move between virtual machines executing on a hypervisor that is itself executing on a multi-core platform. The hypervisor controls access to the processor, the memory and shared I/O devices. Yet another scheme is described by Marinescu et al [328]; they are more concerned with partitioning as opposed to resource usage, but they do address distributed heterogeneous architectures. Hypervisors are also used by Cilku and Puschner [129], to give temporal and spacial separation on a multiprocessor platform, and Perez et al. [379] use a hierarchical scheduler to statically partition a wind power mixed criticality embedded system requiring certification under the IEC-61508 standard. A hypervisor for a mixed criticality on-board satellite software system is discussed by Salazar et al. [15, 399] and one for general control system is addressed by Crespo et al [133]. The issue of minimising the overheads of a hypervisor is addressed by Blin et al. [88].

#### 5.5 Cyber Physical Systems and Internet of Things

In parallel with the development of a distinct branch of research covering MCS has been the identification of Cyber Physical Systems (CPS) as a useful focus for system development. Not surprisingly it has been noted that many CPS are also mixed criticality. For example Schneider et al. [406] note that many CPS are a combination of deadline-critical and QoS-critical tasks. They propose a layered scheme in which QoS is maximised while hard deadline tasks are guaranteed. Izosimov and Levholt [262] use a safety-critical CPS to explore how metrics can be used to map potential hazards and risk from top level design down to mixed criticality components on a multi-core architecture. Issues of composability within an open CPS are introduced in the short paper by Lee et al. [296].