# A Refinement Strategy for Circus

Ana Cavalcanti<sup>1</sup>, Augusto Sampaio<sup>2</sup> and Jim Woodcock<sup>3</sup>

$^1\,$ Computing Laboratory, University of Kent at Canterbury, C<br/>anterbury, CT2 7NF, England $^2\,$ Centro de Informática, Universidade Federal de Pernambuco, P.O. Box 7851, 50740-540, Recife PE, Brazil

Abstract. We present a refinement strategy for *Circus*, which is the combination of Z, CSP, and the refinement calculus in the setting of Hoare & He's unifying theories of programming. The strategy unifies the theories of refinement for processes and their constituent actions, and provides a coherent technique for the stepwise refinement of concurrent and distributed programs involving rich data structures. This kind of development is carried out using *Circus*'s refinement calculus, and we describe some of its laws for the simultaneous refinement of state and control behaviour, including the splitting of a process into parallel subcomponents. We illustrate the strategy and the laws using a case study that shows the complete development of a small distributed program.

## 1 Introduction

The last twenty years have seen the development and application of various formal methods for software engineering, typified by the state-based and the process algebraic schools. In the state-based approach, a model is constructed of the desired system, avoiding incidental details and concentrating only on essential properties; successive models are constructed, in ever-more detail, until an implementation is reached. For correctness, the models must be related by some well-understood refinement relation. The most prominent members of this school of development are VDM [15], Z [24, 28], and the refinement calculus [18]. In VDM and Z, emphasis is on specification and data refinement, whilst in the refinement calculus, emphasis is, naturally, on calculation. In the process algebraic approach, systems and components are represented by process behaviour patterns that evolve and interact through atomic events. The most prominent members of the process algebraic school are CCS [17] and CSP [11,21]; the latter has a theory of behavioural refinement.

The two schools started out with complementary objectives: VDM, Z, and the refinement calculus have been used to understand how to specify and develop sequential programs with complex data structures; CCS and CSP have been used to understand complex patterns of concurrency and communication, but with simple data structures. Over the last decade, various attempts have been made to unite the two schools, and produce a method that is suitable for developing concurrent and distributed systems with sophisticated data structures. The first attempts involved understanding data refinement in the context of concurrency and communication [16, 13, 29]. Subsequent attempts focussed on combining particular notations, such as VDM, Z, CCS, and CSP [6, 7, 23, 25].

Most recently, the *Circus* language has been proposed; it is a thorough integration of Z, CSP, and the refinement calculus. The semantics of *Circus* are given in Hoare & He's unifying theories of programming [12], resulting in a notation with a single semantics and a single refinement ordering. The objective was to give a sound basis to the development of concurrent and distributed systems in the calculational style.

In *Circus*, systems are characterised by processes, which group constructs that describe data and control behaviour. Data is defined using mainly the Z notation, and behaviour is characterised by actions, which are defined using Z, CSP, and guarded command constructs.

In previous work [22, 3], we have dealt, separately, with action and process refinement in *Circus*. In that context, we proposed refinement notions and some useful laws. The purpose of this paper is to unify these results, and provide an accompanying iterative development strategy, involving the application of simulation, action and, most importantly, process refinement. In this integrated context, we propose a notion of backwards simulation, in addition to that of forwards simulation provided in [22]. We also provide some new refinement laws for simulation, actions, and processes. We illustrate the refinement strategy through a complete development of a case study which has been only partially addressed before.

In Section 2, we describe the specification of a bounded, reactive, buffer as a means of introducing the *Circus* notation. In Section 3, we explain the notions of refinement in *Circus* for processes and their constituent actions, and the simulation technique; we also describe our strategy for the development

of centralised specifications into distributed implementations. In Section 4, we give laws for piece-wise data refinement. Sections 5 and 6 contain our algebraic laws for the simultaneous refinement of the state and control behaviour of processes and of actions. In Section 7, we illustrate our refinement strategy by showing the complete development of the reactive buffer into a distributed implementation. Finally, in Section 8, we draw our conclusions and discuss related work.

## 2 Circus

A *Circus* program is a list of paragraphs containing process definitions and their ancillary declarations of channels, types, and global constants. We provide a BNF description of the *Circus* syntax later on, but first we introduce *Circus* through an example: a bounded, reactive buffer. We present a specification for this buffer here, and in Section 7 we refine it to obtain a distributed design.

The maximum size of the buffer is a strictly positive constant.

$maxbuff: \mathbb{N}_1$

It takes its inputs and supplies its outputs on two different typed channels.

**channel** *input*, *output* :  $\mathbb{N}$

In *Circus* we use the Z notation to define the state; the attendant operations are actions, which are specified using Z, CSP operators, and the guarded command language. In our example, the process *Buffer* encapsulates two state components: an ordered list of the contents and the size of this list.

```

process Buffer \cong begin

```

```

state BufferState \cong [buff : seq \mathbb{N}; size : 0 ... maxbuff | size = #buff \le maxbuff ]

```

Initially, the buffer is empty; this is specified as a state initialisation action.

$BufferInit \stackrel{\frown}{=} [BufferState' \mid buff' = \langle \rangle \land size' = 0]$

We need to describe the behaviour of the process on input and output. The buffer accepts an input whenever there is space to store the new value; in this case, the element input is appended to the bounded sequence and the size incremented. First, we specify *InputCmd*, which describes the effect of the input on the state; as usual in Z, a schema is used.

InputCmd  $\hat{=}$  [ $\Delta BufferState; x?: \mathbb{N} \mid size < maxbuff \land buff' = buff \land \langle x? \rangle \land size' = size + 1$ ]

The following action, *Input*, describes the constraint on the communication over the channel *input*, and uses the schema action *InputCmd* to specify the state changes.

$Input \stackrel{\frown}{=} size < maxbuff \& input?x \rightarrow InputCmd$

This action is guarded by size < maxbuff: if this condition does not hold, *Input* deadlocks. In contrast, if a precondition of a schema action is not satisfied, its execution diverges (aborts), as usual in Z.

The action  $input?x \rightarrow InputCmd$  is a prefixing in the style of CSP. A new input variable x is introduced, and a value input through the channel input is assigned to it. Afterwards, the action InputCmd is executed.

The *Output* action is enabled when the buffer contains something; it outputs the head of the buffer, and updates the size accordingly.

$$\begin{aligned} OutputCmd &\cong [\Delta BufferState \mid size > 0 \land buff' = tail \ buff \land size' = size - 1] \\ Output &\cong size > 0 \ \& \ output! (head \ buff) \to OutputCmd \end{aligned}$$

An unnamed main action at the end of a process description defines its extensional behaviour as a protocol in terms of the actions over the state. In our example, the main action initialises the buffer and repeatedly offers the choice of input and output.

• BufferInit;  $(\mu X \bullet (Input \Box Output); X)$

$| maxbuff : \mathbb{N}_{1}$ channel input, output :  $\mathbb{N}$ process  $Buffer \cong \mathbf{begin}$ state  $BufferState \cong [buff : seq \mathbb{N}; size : 0 ... maxbuff | size = #buff \le maxbuff ]$   $BufferInit \cong [BufferState' | buff' = \langle \rangle \land size' = 0]$   $InputCmd \cong [\Delta BufferState; x? : \mathbb{N} | size < maxbuff \land buff' = buff \land \langle x? \rangle \land size' = size + 1]$   $Input \cong size < maxbuff \& input?x \rightarrow InputCmd$   $OutputCmd \cong [\Delta BufferState | size > 0 \land buff' = tail buff \land size' = size - 1]$   $Output \cong size > 0 \& output!(head buff) \rightarrow OutputCmd$   $\bullet BufferInit; (\mu X \bullet (Input \Box Output); X)$ end

Fig. 1. Buffer process specification.

#### $\mathbf{end}$

We summarise the complete specification of the buffer process in Figure 1.

In Figure 2 we present the BNF description of the syntax of *Circus*. CircusPar<sup>\*</sup> is a possibly empty list of elements of the syntactic category CircusPar of *Circus* paragraphs; similarly for PPar<sup>\*</sup> (process paragraphs). We use N<sup>+</sup> for a comma-separated list of Z identifiers (elements of N), and similarly for Exp<sup>+</sup>. The syntactic categories Par, Schema-Exp, Exp, Pred, and Decl include the Z paragraphs, schema expressions, expressions, predicates, and declarations defined in [24]. The syntactic category CSExp of channel set expressions contains the empty set {|}, channel enumerations enclosed in {| and |}, and expressions involving the usual set operators. Similarly, NSExp contains sets of state components; in this case the delimiters are ordinary braces.

The *Buffer* example has shown how processes are constructed from actions, but processes may themselves be combined with CSP operators, such as (alphabetised) parallel composition. The meaning of a new process constructed in this way is obtained from the conjunction of the state of the constituent processes and the parallel combination of their main actions.

A perhaps unusual operator available in *Circus* is indexing: a process such as  $i: T \odot P$  behaves like P, but uses different channels. For each channel c of P, we have a fresh channel  $c_i$  that communicates pairs of values: the first element is the index, a value of type T, and the second element is the value originally communicated through c. The instantiation  $(i: T \odot P) \lfloor e \rfloor$  behaves like P, but the first element of the pairs communicated is the value of the index expression e. We also have a renaming operator in *Circus*. For example, in  $P[c_1 := c_2]$ , the communications of P through channel  $c_1$  are done through the channel  $c_2$  instead. An example of the use of the indexing and renaming operators is found in our case study (Section 7).

Parametrised processes are also available in *Circus*. In the process  $x : T \bullet P$ , for instance, x is a parameter that can be used in the specification of P as a value of type T. To use this process, we must instantiate it by providing a value for x, as in  $(x : T \bullet P)(v)$ , where v is a value of type T.

At the level of actions, the *Circus* parallel operator is slightly different from that of CSP. Instead of having simply a synchronisation channel set, we also have two sets that partition all the variables in scope: the state components, and the input and local variables. For instance, we write  $A_1 ||ns_1| C | ns_2|| A_2$ for the parallel composition of  $A_1$  and  $A_2$  synchronising on the channels in the set C, so that  $A_1$  can modify only the variables in  $ns_1$  and, similarly,  $A_2$  can modify just the variables in  $ns_2$ ; both  $A_1$  and  $A_2$  have access to the initial value of the variables in  $ns_1$  and  $ns_2$ . Examples are presented in our case study (Section 7). Sets containing names of state components can be defined to shorten the definition of parallel compositions of actions. The interleaving operator also requires state partitioning sets.

We also have iterated versions of the process and action operators. For example, if P is an indexed process, then  $\|\|i: T \odot P[i]$  is the process defined by interleaving each of the processes P[v] formed by instantiating P with a value v of T. Except for sequence, all the above operators are commutative

| Program              | ::=                              | CircusPar*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CircusPar            | ::=                              | $Par \mid \mathbf{channel} \; CDecl \mid \mathbf{chanset} \; N == CSExp \mid \mathbf{process} \; N \mathrel{\widehat{=}} Proc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CDecl<br>SimpleCDecl | ::=<br>::=                       | SimpleCDecl   SimpleCDecl; CDecl $N^+ \mid N^+$ : Exp   Schema-Exp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CSExp                | ::=                              | $\{\!\mid\} \mid \{\!\mid N^+ \mid\} \mid N \mid CSExp \cup CSExp \mid CSExp \cap CSExp \mid CSExp \setminus CSExp$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Proc                 | ::=<br> <br> <br> <br> <br> <br> | begin PPar* state Schema-Exp PPar* • Action end   NProc; Proc   Proc $\Box$ Proc   Proc $\Box$ ProcProc [[CSExp]] Proc   Proc   Proc   Proc \ CSExpDecl $\odot$ Proc   Proc[Exp <sup>+</sup> ]   Proc[N <sup>+</sup> := N <sup>+</sup> ] ${}^{\circ}$ Decl $\odot$ Proc   $\Box$ Decl $\odot$ Proc   $\Box$ Decl $\odot$ Proc   Decl [[CSExp]] $\odot$ Proc       Decl $\odot$ ProcDecl • Proc   Proc(Exp <sup>+</sup> ) ${}^{\circ}$ Decl • Proc   $\Box$ Decl • Proc   $\Box$ Decl • Proc   Decl • Proc   $\Box$ Decl • Proc   $\Box$ Decl • Proc   Decl • Proc   $\Box$ Decl • Proc   $\Box$ Decl • Proc |

| NSExp                | ::=                              | $\{\} \mid \{N^+\} \mid N \mid NSExp \cup NSExp \mid NSExp \cap NSExp \mid NSExp \setminus NSExp$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PPar                 | ::=                              | $Par \mid N \stackrel{<}{=} Action$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Action               | ::=                              | $Schema-Exp \mid CSPAction \mid Command \mid \mathbf{nameset} \; N == NSExp$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CSPAction            | ::=<br> <br> <br> <br>           | $\begin{array}{l} Skip \mid Stop \mid Chaos \mid Comm \to Action \mid Pred \And Action \\ Action; Action \mid Action \square Action \mid Action \square Action \\ Action \mid [NSExp \mid CSExp \mid NSExp]   Action \mid Action & [NSExp \mid NSExp] \\ Action \setminus CSExp \mid \mu N \bullet Action \mid Decl \bullet Action \mid Action(Exp^+) \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                             |

| Comm<br>CParameter   | ::=<br>::=                       | N CParameter*<br>? N   ? N : Predicate   ! Expression   . Expression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Command              | ::=                              | $N^+:[Pred,Pred]\midN^+:=Exp^+\mid\mathbf{if}\ GActions\ \mathbf{fi}\mid\mathbf{var}\ Decl\bulletAction$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GActions             | ::=                              | $Pred \to Action ~ ~ Pred \to Action ~\square~ GActions$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Fig. 2. Circus syntax

and associative, so there is no concern about the order of the elements of T or about the grouping of the processes. For the sequence operator, we require T to be a sequence and define;  $i: T \odot P\lfloor i \rfloor$  to be the sequence of the processes  $P\lfloor v \rfloor$ , with v taken from T in the order that they appear. For the indexed parallel and interleave operators, we also need to provide the list of synchronising channels, and state partitioning sets.

The semantics of *Circus* [27, 26] is based on Hoare & He's unifying theories of programming [12]: an alphabetised relational model for imperative programming, concurrency, and communication. In this model, distinguished variables are used to describe relevant observations and the relations are defined by predicates over these variables. Decorations are used to differentiate references to the initial value of the variables from those in subsequent observations. As in most refinement theories, the same model is used for specifications and programming constructs, which can be mixed during development.

Refinement is a central notion in the unifying theories of programming, where it is defined as (reverse) implication: if an implementation is to behave satisfactorily, then every observation that we make of it must be permitted by the specification. Formally, a mechanism modelled as a predicate P satisfies a specification S, another predicate, providing that  $[P \Rightarrow S]$ , where the square brackets denote universal quantification over all observation variables. The set of observation variables must be the same for both P and S.

In our work, Z is used as the concrete syntax for the relational model, so that a *Circus* program denotes a Z specification. Each process corresponds to a part of that specification characterised by a state definition. Actions are modelled as operations over this state. The state components are the observation variables, which include the components of the process state and components to model behaviour: stability from divergence (*okay*), termination (*wait*), a history of interaction with the environment (*tr*), and a set of events that can be refused (*ref*). This is a state-based, failures-divergences model, with embedded imperative features.

## **3** Refinement notions and strategy

The basic notion of refinement in *Circus* is that of action refinement; refinement of processes is defined in terms of refinement of main actions. The definition of the relation  $\sqsubseteq_{\mathcal{A}}$  of action refinement is shown below. For simplicity, we identify a *Circus* action with its semantics: a schema specifying a change on the state formed by the components of the state of the process where the action occurs, and the extra observation variables *okay*, *wait*, *tr*, and *ref*. We say that, together, these variables compose the state space of the action.

**Definition 1 (Action refinement).** For actions  $A_1$  and  $A_2$  on the same state space, we define  $A_1 \sqsubseteq_A A_2$  if, and only if,  $[A_2 \Rightarrow A_1]$ .

This relation is a partial order, and the action constructors are monotonic with respect to it. Therefore, we can adopt a piecewise and stepwise refinement technique. Typically, we use the action refinement relation to compare actions of the same process, which, of course, act on the same state space.

Refinement of processes must consider their state and behaviour. Since the main action of a process defines its behaviour, roughly, a process  $P_1$  is refined by a process  $P_2$  if the main action of  $P_1$  is refined by that of  $P_2$ . These actions, however, may act on different state spaces, and so may not be comparable. Since the states are encapsulated, we are to compare the actions we obtain by hiding the components of the state of  $P_1$  and  $P_2$ , as if they were declared locally in a variable block. Process refinement  $(\sqsubseteq_P)$  is, therefore, defined in terms of action refinement of local blocks, whose semantics is given by existential quantification. In the following, we use P.st and P.act to denote the local state and main action of a process P.

**Definition 2 (Process refinement).** We define

$$P_1 \sqsubseteq_{\mathcal{P}} P_2$$

if, and only if,

$(\exists P_1.st; P_1.st' \bullet P_1.act) \sqsubseteq_{\mathcal{A}} (\exists P_2.st; P_2.st' \bullet P_2.act)$

When we hide the local states of the processes, we are left with two actions on the same state space, which contains only *okay*, *wait*, *tr*, and *ref* as components.

Because the state of a process is private, we may change its components and their types during refinement, in much the same way as we can data refine variable blocks and modules in imperative programs [19]. In those contexts, forwards and backwards simulation are well-known techniques of data refinement [10, 14]. Here, we adapt the standard techniques used in Z [28] to handle processes and actions.

In *Circus*, a simulation is a relation between the states of two processes that satisfies a number of properties. For example, in our case study presented in Section 7, the first step is the refinement of the *Buffer* process to introduce a *cache* and a *ring* to represent the internal state. When the buffer is nonempty, the cache stores the head of the buffer. The *ring* is a circular array, modelled as a sequence whose two ends are considered to be joined. We maintain two indices into this array: a *bot*tom and a *top*, to delimit the relevant values. This part of the array is a concrete representation of the tail of the original bounded buffer. Modulo arithmetic is used to increment *bot* and *top*; in Z sequence indices start at 1. The constant *maxring*, defined as *maxbuff* -1, gives the bound for the ring. In the new process, the state is defined as follows.

$\begin{array}{l} CBufferState \\ size: 0 \dots maxbuff; \ ringsize: 0 \dots maxring \\ cache: \mathbb{N}; \ ring: seq \mathbb{N} \\ top, bot: 1 \dots maxring \\ \hline ringsize \ mod \ maxring = (top - bot) \ mod \ maxring \\ ringsize = max\{0, size - 1\} \\ \#ring = maxring \end{array}$

There is a subtle situation when the *bot* tom and the *top* indices coincide; in this case it is not possible to distinguish whether the ring has reached its maximum storage capacity or whether it is empty. As a consequence, we need to keep a separate record of the number *ringsize* of values stored in the ring.

With this new state, all the actions of the original abstract *Buffer* process need to be changed accordingly. In order to justify the refinement, we provide a simulation between the state of the original buffer and the new state, much in the same way as we do when we data refine Z specifications. In our example, the simulation (or retrieve) relation is as follows. We use a shift operator:  $n \ll a$  shifts the (circular) array a by n positions. For the sake of conciseness, we omit the simple inductive definition of this operator.

$$RetrBuffer \cong [BufferState; CBufferState | buff = (1 ... size) \triangleleft (\langle cache \rangle \cap ((bot - 1) \ll ring))]$$

If we shift the *ring* so that the oldest element at *bot* occurs at position 1, concatenate the *cache* at the front of the resulting array, and restrict everything to the first *size* elements, then we have the abstract buffer.

To prove that *RetrBuffer* is indeed a simulation, we have to show that it satisfies a few properties. We define below the restrictions for actions and processes. We actually consider a relation that involves, besides the states of the processes, a local state that can include input and local variables in scope, and any additional information inferred from guards and conditionals in context.

This context is easily defined by induction on the structure of the actions. For example, the context for actions like *Skip* and *Stop* is a schema with an empty declaration and predicate *true*. For a schema expression, the context contains the declaration of the input and output variables, if any. For a guarded action, the context is enriched by conjoining the guard to its predicate. We omit further discussion of contexts in this paper, for the sake of simplicity.

**Definition 3 (Forwards simulation).** A forwards simulation between actions  $A_1$  and  $A_2$  of processes  $P_1$  and  $P_2$ , with local state L, is a relation R between  $P_1$ .st,  $P_2$ .st, and L, satisfying

- 1. (feasibility)  $\forall P_2.st; L \bullet (\exists P_1.st \bullet R)$

- 2. (correctness)  $\forall P_1.st; P_2.st; P_2.st'; L \bullet R \land A_2 \Rightarrow (\exists P_1.st'; L' \bullet R' \land A_1)$

In this case, we write  $A_1 \leq_{P_1,P_2,R,L} A_2$  and say that the action  $A_2$  simulates the action  $A_1$ , according to the simulation R, and in a state extended by L. When clear from the context, we omit the subscripts. A forwards simulation between  $P_1$  and  $P_2$  is a forwards simulation between their main actions.  $\Box$

In this definition, there is no applicability requirement concerning preconditions, as would usually be found in the definition of forwards simulation; this is because actions are total. An action that is executed outside its preconditions diverges, but this does not mean that its behaviour is arbitrary. Implicitly, it is guaranteed that the state invariant is maintained, and that arbitrary new synchronisations and communications can be observed, but no past observations are affected. Another possibly surprising aspect of Definition 3 is the fact that we do not impose any specific conditions on the initialisation. It is not necessarily the case that there is a separate initialisation action and, even if there is, it has to be explicitly included in the main action, as illustrated in Figure 1.

A theorem reproduced below and proved in [22] ensures that, if we provide a forwards simulation between processes  $P_1$  and  $P_2$ , then we can substitute  $P_2$  for  $P_1$  in a program.

**Theorem 1** (Forwards simulation is sound). When a forwards simulation exists between two processes  $P_1$  and  $P_2$ , we also have that  $P_1 \sqsubseteq_{\mathcal{P}} P_2$ .

In the next section we present laws that support the refinement of a process using simulation. For backwards simulation, we have similar definitions and results; first, we present the definition.

**Definition 4 (Backwards simulation).** A backwards simulation between actions  $A_1$  and  $A_2$  of processes  $P_1$  and  $P_2$ , with local state L, is a relation R between  $P_1$ .st,  $P_2$ .st, and L, satisfying

1. (feasibility)  $\forall P_2.st; L \bullet (\exists P_1.st \bullet R)$

2. (correctness)  $\forall P_1.st'; P_2.st; P_2.st'; L' \bullet R' \land A_2 \Rightarrow (\exists P_1.st; L \bullet R \land A_1)$

A backwards simulation between  $P_1$  and  $P_2$  is a backwards simulation between their main actions.  $\Box$

A soundness theorem can be proved in much the same way as in the case of forwards simulation; the challenge is to realise the need for the feasibility restriction, which is the same for both forms of simulation.

Although we have notions of forwards and backwards simulation, we do not have a completeness result due to the presence of unbounded nondeterminism. The technical difficulties involved are discussed in [9].

The refinement notions support the transformation of *Circus* processes for several purposes, such as to show the equivalence or refinement of processes, to carry out optimisations, or to justify change of data representation. Here, we are interested in a development strategy that we discuss in the sequel. The strategy is based on laws of simulation, and action and process refinement, which we present in Sections 4 to 6.

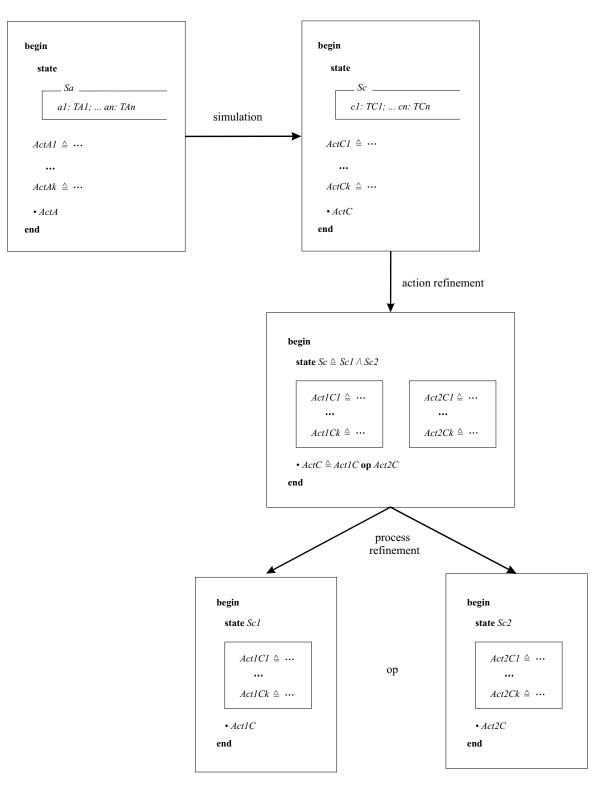

The strategy includes (possibly several iterations) of the following steps (see Figure 3):

- use of simulation to introduce the elements of the concrete system state;

- algorithmic refinement of actions for partitioning the process state space and actions; and

- process refinement (decomposition).

Although simple, the iterated application of these steps can effectively serve as a tool to guide and transform an abstract, and usually centralised, specification into a concrete distributed solution of the system.

Assuming a centralised process specification as the starting point of the development, the first two steps of the strategy are used to reorganise the internal structure of the process. In Figure 3, the first specification is a centralised process with state components  $a1, \ldots, an$ , actions  $ActA1, \ldots, ActAk$ , and main action ActA. Simulation lays the ground for the introduction of concrete state elements  $c1, \ldots, cn$ , which compose the state of the second process in Figure 3. The actions are also changed to operate on the modified state.

Action refinement allows the partitioning of the state space and the accompanying actions, in such a way that each partition groups some state elements and the actions which access (read or update) these elements. The resulting structure clearly reflects the fact that each partition will become an independent process. The third process in Figure 3 illustrates this partitioning. The state Sc is defined by the conjunction of two state schemas Sc1 and Sc2; sets of actions that operate independently on Sc1 and on Sc2 can be clearly identified; and the main action is defined as a combination of two of these independent actions: Act1C and Act2C. In the next step, these become the main actions of the partitioned processes.

The upgrade of a partition into a process is precisely captured in the third step of the strategy. The resulting processes are combined in the same way as their main actions were in the previous process.

It is worth emphasising that several iterations might be necessary, even in a medium-sized development, since a process resulting from one decomposition can itself be further decomposed into other processes, and so on. An interesting issue is that the development of a distributed system does not necessarily start with a centralised specification. Nonetheless, even in such a more pragmatic scenario, some process decomposition is usually essential in order to progress towards the final implementation, which needs to satisfy non-functional requirements like efficiency. Therefore, the strategy can be applied to every

Fig. 3. Iteration of the refinement strategy

process that needs decomposing, just like it is applicable when the starting point is a centralised process specification.

An iteration of the strategy does not need to follow the above sequence of steps strictly. For example, a simulation step can subsume some action refinement. On the other hand, several applications of a given step (like data or action refinement) might be convenient for modularising the development. It might be even the case that a given process is ready for decomposition from start, when its internal structure is already partitioned. In this case, only the third step of the strategy would be necessary. An iteration of the strategy is characterised by one application of the process refinement step: whether several, one, or no application of simulation and action refinement is needed depends on the particular development at hand.

## 4 Laws of simulation

Although the definition of simulation and its soundness property give us the basis for a data refinement technique, in practice, we need laws to carry out data refinement in a stepwise way. The laws in the sequel provide support to prove that a relation R is indeed a forwards simulation. Using these laws, we can justify proving simulation for schema actions, in much the same way as we do in Z. Moreover, we are able to preserve the structure of the actions of the original process  $P_1$  in the definition of the new process  $P_2$ .

The primitive actions *Skip*, *Stop*, and *Chaos* are not affected by forwards simulation. For instance  $Skip \leq Skip$ , for any  $P_1$ ,  $P_2$ , R, and L, which we omit. For schema actions, the provisos are those in the standard Z rule, which is a rather pleasing result in terms of using well-established techniques.

#### Law 41 (Schema Expressions)

$$ASExp \preceq CSExp$$

#### provided

- $\forall P_1.st; P_2.st; L \bullet R \land \text{pre } ASExp \Rightarrow \text{pre } CSExp$

- $\forall P_1.st; P_2.st; P_2.st'; L \bullet R \land \text{pre } ASExp \land CSExp \Rightarrow (\exists P_1.st'; L' \bullet R' \land ASExp)$

We refrain from presenting the particular case of initialisation operations and functional data refinement. Since the more generic rule presented above holds, the usual results follow.

This law includes an applicability condition, which does not appear in the definition of forwards simulation. This is because the definition is concerned with the semantics of actions, which are total operations on the state that includes the extra observation variables *okay*, *wait*, *tr*, and *ref*. An action described by a schema expression is an operation over the process state and it is not necessarily total. The proof of soundness for this and several other laws presented here can be found in [22, 3].

As already mentioned, forwards simulation distributes through the other constructs. Below, we present the rule for an input prefix.

#### Law 42 (Input prefix distribution)

$$c?x \to A_1 \preceq c?x \to A_2$$

provided  $A_1 \preceq A_2$

For output prefixing, we need to relate the abstract and concrete expressions defining the output value.

### Law 43 (Output prefix distribution)

$$c!ae \to A_1 \preceq c!ce \to A_2$$

provided

•

$$\forall P_1.st; P_2.st; L \bullet R \Rightarrow ae = ce$$

•

$$A_1 \preceq A_2$$

The concrete and abstract values have to be equal, with respect to the retrieve relation. As far as we know, this characterisation of equality for expressions modulo a retrieve relation is original. For guarded actions, we also need to relate the abstract and the concrete predicates that define the guard.

#### Law 44 (Guard distribution)

$$ag \& A_1 \preceq cg \& A_2$$

#### provided

•  $\forall P_1.st; P_2.st; L \bullet R \Rightarrow (ag \Leftrightarrow cg)$

•

$$A_1 \preceq A_2$$

The proviso is similar to that of Law 43. For the other constructs, we have straightforward distribution laws.

#### Law 45 (Sequence distribution)

$$A_1; A_2 \preceq B_1; B_2$$

provided

•

$$A_1 \preceq B_1$$

•  $A_2 \preceq B_2$

Law 46 (External choice distribution)

$$A_1 \Box A_2 \preceq B_1 \Box B_2$$

#### provided

•

$$A_1 \preceq B_1$$

•  $A_2 \preceq B_2$

The law for parallelism uses the fact that the actions affect disjoint parts of the state; there is no interference.

## Law 47 (Parallelism distribution)

$$A_1 \llbracket ns_1 \mid cs \mid ns_2 \rrbracket A_2 \preceq B_1 \llbracket ns_1 \mid cs \mid ns_2 \rrbracket B_2$$

#### provided

•

$$A_1 \leq B_1$$

•  $A_2 \leq B_2$

The fact that  $ns_1$  and  $ns_2$  partition the state is a well-formedness condition for the parallel operator. For recursion, we also have a simple result.

#### Law 48 (Recursion distribution)

$$\mu X \bullet F(A) \preceq \mu X \bullet F(B)$$

## **provided** $A \preceq B$

We use F to stand for a context: a function on actions that determines the body of the recursion.

Based on this set of laws, we can conclude that forwards simulation distributes through the structure of arbitrary actions. Our case study (Section 7) illustrates the use of these laws; we give a new action on the state defined by *ControllerState* and deduce, from applications of Law 41 to the schema expressions, that the whole action simulates the original main action of Buffer according to RetrBuffer. Simulation is also used in a later stage of the development.

The laws for backwards simulation are very similar to those above, consequently, we present below only the law for schema expressions.

#### Law 49 (Schema Expressions)

$ASExp \preceq CSExp$

#### provided

•  $\forall P_2.st; L \bullet (\forall P_1.st \bullet R \Rightarrow \text{pre } ASExp) \Rightarrow \text{pre } CSExp$ •  $\forall P_2.st; L \bullet (\forall P_1.st \bullet R \Rightarrow \text{pre } ASExp) \Rightarrow$  $(\forall P_1.st'; P_2.st'; L' \bullet CSExp \land R' \Rightarrow (\exists P_1.st \bullet R \land ASExp))$

Again, we have proof obligations similar to those needed for establishing refinement of Z specifications.

## 5 Process Refinement

In this section we propose refinement laws for processes. These laws deal simultaneously with state and control behaviour. As further discussed in Section 7, our approach to the refinement of *Circus* specifications is guided by the progressive and incremental distribution of a specification originally centralised. Surprisingly, perhaps, such a strategy can be supported by simple laws that allow the partitioning of processes.

We present two families of refinement laws, but beforehand we state a basic law that allows the introduction of a new process declaration pd as part of the sequence of paragraphs of a *Circus* program cp.

#### Law 51 (Process declaration introduction)

cp = pd cp

**provided** the process declared in *pd* is not referenced in *cp*.

This law can be justified in much the same way as the introduction of fresh variables and procedure declarations in an imperative program, or new class declarations in an object-oriented program. As the declared process is assumed to be unused, its introduction has no effect whatsoever. The importance of this apparently innocuous law becomes evident in the sequel.

#### 5.1 Process splitting

The first family of process partitioning laws, called *process splitting*, apply to processes whose state components can be partitioned in such a way that each partition has its own set of process paragraphs. The result is three processes: each of the first two includes a partition of the state and the corresponding paragraphs, and the third process, defined in terms of the first two, has the same behaviour as the original one.

In what follows, we assume that pd stands for the process declaration below, where we use Q.pps and R.pps to stand for the process paragraphs of the processes Q and R; and F for an action context which must also make sense as a function on processes, according to the *Circus* syntax.

```

process P \cong begin

state State \cong Q.st \land R.st

Q.pps \uparrow R.st

R.pps \uparrow Q.st

\bullet F(Q.act, R.act)

end

```

The state of P is defined as the conjunction of two other state schemas: Q.st and R.st. The actions of P are  $Q.pps \uparrow R.st$  and  $R.pps \uparrow Q.st$ , which handle the partitions of the state separately. In  $Q.pps \uparrow R.st$ , each schema expression in Q.pps is conjoined with  $\Xi R.st$ . This means that these process paragraphs do not change the state components of R.st; similarly for  $R.pps \uparrow Q.st$ .

We say that a process with the above internal structure is partitioned. We call a partition a group of paragraphs formed by a schema declaring a subset of the state components, together with the actions that use or constrain only these state components. For example, in P above, Q.st and  $Q.pps \uparrow R.st$  form a partition; and so does R.st together with  $R.pps \uparrow Q.st$ . The law below applies to a partitioned process.

#### Law 52 (Process splitting)

Let qd and rd stand for the declarations of the processes Q and R, determined by Q.st, Q.pps, and Q.act, and R.st, R.pps, and R.act, respectively, and pd stand for the process declaration above. Then

$pd = (qd \ rd \ \mathbf{process} \ P \cong F(Q, R))$

**provided** Q.pps and R.pps are disjoint with respect to R.st and Q.st.

Two sets of process paragraphs  $pps_1$  and  $pps_2$  are disjoint with respect to states  $s_1$  and  $s_2$  if, and only if, no command nor CSP action expression in  $pps_1$  refers to components of  $s_2$  or to paragraph names in  $pps_2$ ; similarly, for  $pps_2$  and components of  $s_1$ .

This law can be informally justified by first adding the declarations qd and rd to the left-hand side (as stated by Law 51), and then promoting the context F from main actions to the corresponding processes.

#### 5.2 Process indexing

The second family of laws applies to processes defined using Z's promotion technique. It is based on defining the specification of an abstract data type with its operations and then using this as the type of the elements of a more elaborate data structure like, for instance, a set, a sequence, or a map. For example, one can specify a bank account with its operations and then specify the bank itself as a collection of accounts. Promotion allows an elegant specification of such patterns. The name of the technique comes from the fact that the operations on the collection are defined in terms of those on the element type and a promotion schema.

By convention, the element type is referred to as local, whereas the collection is called global. When the local type is completely encapsulated in the global type, we say that the promotion is free; otherwise it is called constrained [28]. Here we are concerned solely with free promotions.

The proposed family of laws refines a specification structured using a free promotion to an indexed family of processes, each one representing an element of the local type. Considering the bank account example, the law would transform each account into an individual process, and the bank itself into an indexed family of such processes, combined using the interleaving operator.

One of the contributions of this work is to extend Z's promotion technique to *Circus* actions. Below we give an inductive definition of the relevant patterns; L stands for the local process, G for the global process, and *Promotion* for the promotion schema. We observe that we are promoting a process and not a simple abstract data type as in Z; however, we adopt the standard terminology and refer to local and global processes.

For simplicity, we assume that the global state is a function f from elements of an arbitrary type *Range* to elements of the local state; so, a local element is identified in the global state as f *i*. Promotion of schema expressions is as in Z.

$\mathbf{promote}(SExp) \cong \exists \Delta L.st \bullet SExp \land Promotion$

The promotion of Skip, Stop, and Chaos leaves them unchanged.

$\mathbf{promote}(A) \cong A, \quad \text{for } A \in \{Skip, Stop, Chaos \}$

To promote a communication c.e, where e is a reference to an element of the local state, we need to receive an extra value: the position i of e in the collection. Therefore, for each channel c, there is a corresponding promoted channel pc that communicates a pair formed by the identifier and the value.

$\mathbf{promote}(c.e \to A) \cong pc?i.\mathbf{promote}(e) \to \mathbf{promote}(A)$  provided e is a component of L.st

To promote any other communication, we only promote the communicated expression.

$\mathbf{promote}(c.e \to A) \cong c.\mathbf{promote}(e) \to \mathbf{promote}(A)$  provided *e* is not a component of *L.st*

Promotion for expressions is defined below; for the other forms of prefixing, the definition is similar. Promotion distributes through the other action operators. For a guarded action, we need to promote the guard. Promotion of predicates has an inductive definition based on promotion of expressions. For parallelism and hiding, the channels are replaced with corresponding promoted channels. If a variable x is not a local state component, it does not need to be changed.

$\mathbf{promote}(x) \cong x$ , provided x is not a component of L.st

If it is, then we need to access it through the global state. We assume that the position of x in the collection is given by i. This information is received as input, and can be regarded as an extra parameter for **promote**, which we omit for simplicity.

$$\mathbf{promote}(x) \cong (f \ i).x, \quad \text{if } x \text{ is a component of } L.st$$

Finally, promotion distributes through the expression operators; the simple but lengthy definition is omitted. If the local state includes components x, y, and z, for instance, a promoted assignment like  $(f \ i).x := e$  is an abbreviation for  $f := f \oplus \{l : L.st \mid l.x = e \land l.y = (f \ i).y \land l.z = (f \ i).z \bullet i \mapsto l\}$ .

Promotion of multiple assignments may lead to aliasing if more than one component of the local state is being updated. For example, promotion of x, y := 2, 3 leads to  $(f \ i).x, (f \ i).y := 2, 3$ . A specification statement with a frame containing x and y is also problematic, as promotion leads to restrictions on  $(f \ i).x$  and  $(f \ i).y$  (and  $(f' \ i).x$  and  $(f' \ i).y$ ), and we need to promote these restrictions to f (and f'). We assume that actions like these are not used.

In the sequel, we assume that gd stands for the following process declaration. The family of process indexing laws applies to processes of this form.

```

process G \cong begin

state State \cong [f : Range \leftrightarrow L.st \mid pred]

L.action_k \uparrow State

L.act \cong \mu X \bullet F(L.action_k); X

Promotion \cong [\Delta L.st; \Delta State; i? : Range \mid i? \in \text{dom} f \land \theta L.st = f \ i? \land f' = f \oplus \{i? \mapsto \theta L.st'\}]

action_k \cong \text{promote}(L.action_k)

\bullet (\mu X \bullet F(action_k); X)

```

end

As discussed before, the global state component is assumed to be a function from *Range* to a local state L.st. Actions  $L.action_k$  over the local state do not affect the global state. The main local action L.act is defined recursively, as is the main global action. Both have the same structure, but the former uses the actions  $L.action_k$  on the local states, and the latter, the corresponding promoted actions  $action_k$ . There is a promoted action  $action_k$  for every local action  $L.action_k$ . We note that for each channel c used by the  $action_k$ , the corresponding promoted action uses a corresponding promoted channel pc. A topic for further work is the generalisation of the process indexing family of laws in terms of the data structure used in the global state and the main action of both the local and the global states.

We also consider the declaration *ild* below of the indexed process *IL*.

**process**  $IL \stackrel{\frown}{=} i : Range \odot L[c\_i := pc]$

The process  $i: Range \odot L$  acts on indexed channels  $c_i$ , where L acts on a channel c. Like the promoted channels pc used in P, they communicate pairs of values: the index and the original value. Above, we rename each channel  $c_i$  to pc. In this way, we can use IL in the refinement of P.

The family of laws for process indexing is as follows. We use the iterated interleaving operator; the iteration index i, whose value ranges in the set *Range*, is used to instantiate the *IL* process. In this way, we interleave several copies of the *IL* process, with each copy communicating a different index in *Range*.

#### Law 53 (Process indexing)

Let gd and ild be the process declarations above, and let ld be the declaration of the process L. Then,

$gd = ld \ ild \ \mathbf{process} \ G \cong ||| \ i : Range \odot IL| \ i|$

provided L.pps and G.pps are disjoint with respect to L.st and G.st.

The local state is available through the indexed processes *IL*. Due to interleaving, there is no interference among the individual elements of the collection.

## 6 Action Refinement

Apart from data refining processes, we are also interested in algorithmically refining actions. The result below justifies the use of action refinement (Definition 1).

**Theorem 2 (Soundness of action refinement).** Suppose we have a process P with actions  $A_1$  and  $A_2$ . If  $A_1 \sqsubseteq_A A_2$ , then the identity is a forwards simulation between  $A_1$  and  $A_2$ .

This theorem is proved in [22]. It is a consequence of this theorem that we can refine a process by refining its actions. With this result, laws of CSP and Z, for which we have a calculus called ZRC [4], are relevant.

We concentrate here, however, on the laws that relate Z, guarded commands, and CSP constructs, which are novel. In the sequel, we present a few of them; others are listed in Appendix A. As the laws available in the literature for CSP are mostly aimed at characterising its algebraic semantics, we also need new laws of CSP; some are included in Appendix A.

The first set of laws that we present are related to guarded commands. The first law allows us to use a property assured by an assumption as a guard. An assumption  $\{ pre \}$  is a special specification statement : [pre, true]. This command does nothing if pre holds, and aborts, otherwise.

#### Law 61 (Guard Introduction—Assumption)

$$\{g\}; A = \{g\}; g \& A$$

If g does not hold, both commands above abort; if g does hold, then its introduction as a guard of A has no effect. In other words, as g is already guaranteed to hold by the assumption, we can introduce it as a guard, as no extra possibility of deadlock is introduced.

Our second law allows us to eliminate a guard, in the presence of an assumption.

#### Law 62 (Assumption/Guard—Elimination 1)

$\{g_1\}; (g_2 \& A) \sqsubseteq \{g_1\}; A$

provided  $g_1 \Rightarrow g_2$

If  $g_1$  is such that its validity guarantees that the guard holds, then we can eliminate the guard. Other laws presented in Appendix A (Laws A12 and A13) consider the case in which the assumption guarantees that the guard does not hold, and the possibility of modifying a guard in the presence of an assumption.

We also have new laws that handle guarded actions. The first of these laws introduces a choice of guarded actions from a schema expression *SExp*.

#### Law 63 (Guard Introduction—Schema Expression)

$$SExp \subseteq \Box i \bullet g_i \& SExp \land [State \mid g_i]$$

**provided** pre  $SExp \Rightarrow \bigvee i \bullet g_i$

The proviso guarantees that, if the precondition of SExp holds, then at least one of the guards is enabled. In this case, an action associated with one of the enabled guards  $g_i$  is arbitrarily chosen for execution. The behaviour of this action is given by SExp itself, and so we know that the original behaviour is attained; however, we conjoin SExp with a schema that records that  $g_i$  holds. This may be useful in further refining SExp. If the precondition of SExp does not hold, SExp diverges and  $\Box i \bullet g_i \& SExp \land [State \mid g_i]$  may block. Therefore, we have a refinement as well.

If a schema action is expressed as a disjunction, and it is guarded by the precondition of one of the disjuncts, then the other disjunct can be eliminated.

### Law 64 (Schema Disjunction Elimination)

pre  $SExp_1 \& (SExp_1 \lor SExp_2) \sqsubseteq$  pre  $SExp_1 \& SExp_1$

This law is a refinement because, in general,  $SExp_1 \vee SExp_2$  allows more nondeterminism than its disjunct  $SExp_1$ . In Appendix A there are a number of laws for manipulating guards: combining, distributing, and eliminating them.

We also have laws to handle assumptions. First, they distribute over external choice.

## Law 65 (Assumption/External Choice—Distribution)

$\{p\}; (A_1 \Box A_2) = (\{p\}; A_1) \Box (\{p\}; A_2)$

They also distribute over internal choice, parallelism, and interleaving. Other laws are already listed as part of ZRC. Two laws used in our case study to introduce and eliminate assumptions are in Appendix A.

A refinement calculus needs to provide a way of introducing programming constructs from specifications. ZRC includes laws to introduce guarded command constructs from schema expressions. Law 63 gives a way of introducing a guarded external choice. The following two laws are concerned with the introduction of sequence and parallelism. In the provisos, we use new notation. The function  $\alpha$  gives the set of components of a given schema; it can also be applied to a declaration. The function FV defines the set of free variables of a predicate or expression; DFV determines the set of dashed free variables of a given the set of undashed free variables of a predicate.

#### Law 66 (Sequence Introduction—Schema Expression)

$\begin{bmatrix} \Delta S_1; \ \Delta S_2; \ i?: T \mid preS_1 \land preS_2 \land CS_1 \land CS_2 \end{bmatrix}$  $\begin{bmatrix} \Delta S_1; \ \Xi S_2; \ i?: T \mid preS_1 \land CS_1 \end{bmatrix}; \ \begin{bmatrix} \Xi S_1; \ \Delta S_2; \ i?: T \mid preS_2 \land CS_2 \end{bmatrix}$

syntactic restrictions

\_

- $\alpha(S_1) \cap \alpha(S_2) = \emptyset;$

- $FV(preS_1) \subseteq \alpha(S_1) \cup \{i?\};$

- $FV(preS_2) \subseteq \alpha(S_2) \cup \{i?\};$

- $DFV(CS_1) \subseteq \alpha(S'_1);$

- $DFV(CS_2) \subseteq \alpha(S'_2);$

- $UDFV(CS_2) \cap DFV(CS_1) = \emptyset.$

This law applies to a schema action over a state composed of two disjoint sets of components specified in the schemas  $S_1$  and  $S_2$ . The precondition of the action can be expressed as the conjunction of conditions  $preS_1$  and  $preS_2$  over the different parts of the state and the input variable(s). Also, the updates on the state are expressed as a conjunction of conditions  $CS_1$  and  $CS_2$  over the final values of the disjoint parts of the state.

The application of this law introduces a sequence of schema actions that update the disjoint parts of the state separately. An extra restriction is required: the final values of the state components of  $S_2$  do not depend on the initial values of those of  $S_1$ , as these are potentially changed by the first action in the sequence.

There are no output variables. If we include them, we have to distinguish their specification and determine which action in the sequence is going to produce the output.

ZRC already includes laws to introduce sequences from specifications. This new law is needed in the context of the development of *Circus* programs because it supports the partitioning of the state space of actions. It introduces actions that update disjoint parts of the state.

The next law is concerned with the introduction of parallelism, again from a schema expression. It may seem slightly artificial to introduce communication between schema actions. We must have in mind, however, that these laws are used in stepwise developments, were the schemas are further developed and processes are split. So, the introduction of communication is an interesting step towards a more elaborate structure. This point is illustrated in examples, in the next section.

#### Law 67 (Parallelism Introduction—Schema Expression)

$[\Delta S_1; \Delta S_2; i?: T \mid CS_1(i?, s_2) \land CS_2]$

$$\begin{array}{l} (c?j?s \to [\Delta S_1; \ \Delta S_2; \ j?: \ T; \ s?: \ U \ | \ CS_1(j?, s?)] \\ & \quad |[\alpha(S_1) \ | \ \{]c]\} \ | \ \alpha(S2)]| \\ c!i!s_2 \to [\Delta S_1; \ \Delta S_2 \ | \ CS_2]) \setminus \{]c\} \end{array}$$

#### syntactic restrictions

- $\alpha(S_1) \cap \alpha(S_2) = \emptyset;$

- *i* is an input variable in scope;

- $s_2 \in \alpha(S_2)$  and  $s_2$  has type U;

- $FV(CS_1) \subseteq \alpha(\Delta S_1) \cup \{i?, s_2\};$

- $FV(CS_2) \subseteq \alpha(\Delta S_2);$

- c is a valid channel of type  $T \times U$ .

Like Law 66, this law applies to a schema action over states composed by the conjunction of state schemas  $S_1$  and  $S_2$  with disjoint sets of components. This action takes an input *i*? used to update the state  $S_1$ , but not  $S_2$ . The updates of the state are given by the conjunction of  $CS_1$  and  $CS_2$ ; the former defines the updates on  $S_1$  and the latter, those on  $S_2$ . The updates on  $S_1$  depend on the component  $s_2$  of  $S_2$ , but the updates on  $S_2$  do not depend on  $S_1$ . We use the notation  $P(e_1)$  for a predicate P that potentially includes occurrences of an expression  $e_1$ ; later references to  $P(e_2)$  denote the result of replacing  $e_1$  with  $e_2$  in P.

With the application of the law above, we introduce a parallel composition, in which the disjoint parts of the state are updated separately by different schema actions, each restricted to the relevant part of the state. The hidden channel c is used to communicate the input value from one action to another, as well as the state component  $s_2$  that  $CS_1$  uses from  $S_2$ . The channel c, of course, needs to have been previously declared and have the appropriate type.

The value of the input variable i and of  $s_2$  is sent by the second action to the first one using channel c. This communication introduces new input variables j and s, that are used by the first action, instead of i? and  $s_2$ . Since the second action does not make use of i?, it is not in its declaration part.

An important concern in the development of *Circus* programs is the parallelisation of actions and, as a consequence, processes. We present next a law that transforms a sequence into a parallelism. The interesting point about this law is that we have to make sure the transformation does not affect either state transformations or communications.

In the following we use some new notation. The function usedC gives the set of channels referred in a given action. The function usedV gives the set of used variables: read, but not written. The function wrtV gives the set of variables written by a given action. In the case of a schema expression, wrtV actually gives the set of variables constrained by the schema. The definition is as follows.

$$wrtV(SExp) = \{v' : DFV(SExp) \mid SExp \neq (\exists v' : T \bullet SExp) \land [v, v' : T \mid v' = v] \bullet v\}$$

We use v' to denote the list  $v'_1, \ldots, v'_n$  of dashed free variables in SExp, and v to denote the corresponding list of undecorated variables  $v_1, \ldots, v_n$ . The notation v' : T stands for the declaration  $v_1 : T_1; \ldots; v_n : T_n$  of each of the variables in v' with the corresponding types as defined in SExp. Informally, if we hide v' in SExp and include it back in the signature, we obtain a different schema. This means exactly that the final value of v is changed by SExp.

It is unfortunate that wrtV is not a purely syntactic function, as its calculation for schema expressions involves theorem proving. On the other hand, a tool can take the pragmatic approach of considering the whole of the state components as the set of written variables of a schema action, and request help from the user only if this worst-view approach fails.

#### Law 68 (Parallelism Introduction—Sequence 1)

$A_1; A_2(e) \sqsubseteq ((A_1; c!e \rightarrow Skip) \| \overline{wrtV(A_2)} | \{ c\} | wrtV(A_2) \| c?y \rightarrow A_2(y)) \setminus \{ c\} \}$

#### syntactic restrictions

- c is a valid channel of type T;

- $c \notin usedC(A_1) \cup usedC(A_2);$

- $y \notin FV(A_2)$ .

#### provided

•  $wrtV(A_1) \cap usedV(A_2) = \emptyset;$

•

$$FV(e) \cap wrtV(A_2 \ before \ e) = \emptyset.$$

To preserve the execution order, this law introduces a communication through a new hidden channel c with a new input variable y. This communication removes direct access of  $A_2$  to the expression e. Even though the order of execution is preserved, in a parallelism both actions have access to the initial value of the variables. Therefore, a proviso is needed: the variables changed by the first action are not used by the second one.

This is strictly a refinement law, not an equality. To understand the reason, suppose  $A_1$  is a schema action that leaves the value of a state component v unconstrained, and that  $A_2$  uses this value. In the sequence,  $A_2$  uses the arbitrary value of v, and in the parallelism,  $A_2$  takes the initial value of v.

The sets of partition variables are defined as  $wrtV(A_2)$  and  $wrtV(A_2)$ , where the first is the set of all state components that are not written by  $A_2$ . We observe that  $wrtV(A_1)$  and  $wrtV(A_2)$  are not adequate, as we need to ensure coverage of the whole set of state components. Also,  $wrtV(A_1)$  and  $wrtV(A_1)$  are not appropriate because  $A_2$  has to be given priority to change the value of the variables it modifies. As an example, suppose  $A_1$  changes a state component x to 1, and  $A_2$  changes it to 2; the final value of x has to be 2. The proviso guarantees that  $A_2$  does not use the variable x, but it may update it.

Finally, we need to guarantee that the value of e is not changed by  $A_2$  before it is actually used. The function *before* gives an action that captures the behaviour of its action argument before it has to evaluate the given expression. A worst case view is taken in the definition of *before*, which is defined by recursion on the structure of actions. For example, using the notation SExp[e] to represent the fact that the expression e occurs in the (predicate part of the) schema expression SExp, we have the definition below. We use similar notation for expressions, predicates, actions in general, and others.

SExp[e] before e = Skip

If the expression e occurs in the schema, the resulting action is Skip: the action that occurs before e and has to be evaluated is Skip.

In general, for any action A, if e does not occur in it, the result is A itself.

A before e = A, if e does not occur in A

This covers the actions *Skip*, *Stop*, and *Chaos*, for example.

For prefixing, the definition is as follows.

$(c?x \to A)$  before  $e = c?x \to A$ , if  $x \in FV(e)$  $(c?x \to A)$  before  $e = c?x \to (A \text{ before } e)$ , otherwise

If a free variable x of e is reintroduced locally as an input variable, e cannot occur in its scope, since occurrences of x there are references to the input variable, and not to the same variable mentioned in e. If the input variable is not free in e, we proceed to the prefixed action A.

The definition for the other constructs is not very illuminating, except, perhaps, for sequence.

$(A_1[e]; A_2)$  before  $e = A_1[e]$  before e $(A_1; A_2)$  before  $e = A_1$ ;  $(A_2$  before e), if e does not occur in  $A_1$

If e occurs in the first action, the second one does not need to be considered.

Typically, with the application of Law 68 we want to avoid direct access of  $A_2$  to a state component. So, we consider in Law A20 in Appendix A the particular case in which e is a variable. However, the generality above is necessary, because we work with structured variables, like sequences, and we do not want to communicate the entire component. If we have just a variable, we can have less restrictive provisos.

As we split and combine processes, it is often useful to manipulate channels accordingly. The following law allows us to combine channels: if all communications between two actions occur sequentially through channels  $c_1$  and  $c_2$ , we can use only one channel  $c_3$  to communicate the same values.

#### Law 69 (Channel Combination)

$(A_{1}[c_{1}.com_{1} \rightarrow c_{2}.com_{2} \rightarrow B_{1}] || ns_{1} | \{|c_{1}, c_{2}|\} | ns_{2}|| A_{2}[c_{1}.com_{3} \rightarrow c_{2}.com_{4} \rightarrow B_{2}]) \setminus \{|c_{1}, c_{2}|\}$  $(A_{1}[c_{3}.com_{1}.com_{2} \rightarrow B_{1}] || ns_{1} | \{|c_{3}|\} | ns_{2}|| A_{2}[c_{3}.com_{3}.com_{4} \rightarrow B_{2}]) \setminus \{|c_{3}|\}$

#### syntactic restrictions

=

- all occurrences of  $c_1$  and  $c_2$  in  $A_1$  and  $A_2$  are as explicitly stated;

- $c_3$  is a valid channel of the appropriate type.

Obviously, the new channel has to have the appropriate type to communicate pairs of values: the first element is the value originally communicated by  $c_1$ , and the second, the value communicated by  $c_2$ .

The next laws allow the extension and reduction of channel synchronisation sets.

#### Law 610 (Channel Extension 1)

$$A_1 | [ ns_1 | cs | ns_2 ] | A_2 = A_1 | [ ns_1 | cs \cup \{ c \} | ns_2 ] | A_2$$

**provided**  $c \notin usedC(A_1) \cup usedC(A_2)$

The channel has to be new, in the sense that it is not used in the actions in parallel. Applied from right to left, this law can also be used to reduce channel sets.

The next law is more elaborate: it extends the synchronisation set and uses the new channel to communicate a value e from one of the parallel actions to the other.

#### Law 611 (Channel Extension 2)

$$A_1 \| [ns_1 | cs | ns_2 \| A_2(e) = (c!e \to A_1 \| [ns_1 | cs \cup \{ |c| \} | ns_2 \| c?x \to A_2(x)) \setminus \{ |c| \}$$

#### syntactic restrictions

- *c* is a valid channel of the appropriate type;

- $c \notin usedC(A_1) \cup usedC(A_2);$

- $x \notin FV(A_2)$ .

**provided**  $FV(e) \cap wrtV(A_2 \ before \ e) = \emptyset$

The idea is that the access of  $A_2$  to e is removed. As in Law 68, we have to make sure that the value of e is not changed before it is actually used in  $A_2$ .

The following law eliminates unnecessary extra synchronisation between two parallel actions.

#### Law 612 (Synchronisation Elimination)

$$(\Box \ i \bullet g_i \& c_i.ccom_i \to d_i.acom_i \to A_i) \\ \|[ns_1 \mid cs \cup \{] i \bullet c_i\}\} \mid ns_2] \| \\ (\Box \ i \bullet g_i \& c_i.ccom_i \to d_i.bcom_i \to B_i) \\ = \\ (\Box \ i \bullet d_i.acom_i \to A_i) \|[ns_1 \mid cs \mid ns_2]\| (\Box \ i \bullet g_i \& c_i.ccom_i \to d_i.bcom_i \to B_i) \\ \text{provided} \quad \{i \bullet c_i\} \cap usedC(A_i) \cup usedC(B_i) = \emptyset$$

It is not necessary for parallel actions to synchronise in sequence on  $c_i$  and  $d_i$ . Just one of the synchronisations is necessary to ensure the order of execution of the actions. An important point, of course, is that the communication parameter  $ccom_i$  of c is common to both actions. This means that the communication between them is always possible; any restrictions are imposed by their environment. In other words, even though the channels  $c_i$  are used to communicate values, from the point of view of the parallel actions,

they are just extra synchronisation points. At the same time we eliminate the communications, we can also eliminate the associated guards. If they are false, the guarded action blocks, the communication does not occur, and the matching actions  $d_i.acom_i \rightarrow A_i$  cannot proceed either.

As already mentioned, laws of CSP are also relevant for *Circus*. In our case study, we use some, which are listed in Appendix A. We include laws for prefixing that relate this construct to sequence, choice, parallelism, and interleaving. In those laws, the function  $\alpha$  is applied to a communication; it gives the input variables the communication introduces. These are the variables declared by the communication, which are in scope for the action that follows the communication in a prefixing.

We also have laws for external choice and parallelism. The following is a kind of step law for parallelism, where one of the actions put in parallel is a sequence. The law determines conditions in which the first step is the first action of the sequence.

#### Law 613 (Parallelism/Sequence—Step)

$$(A_1; A_2) [[ns_1 | cs | ns_2]] A_3 = A_1; (A_2 [[ns_1 | cs | ns_2]] A_3)$$

provided

- $initials(A_3) \subseteq cs;$

- $cs \cap usedC(A_1) = \emptyset;$

- $wrtV(A_1) \cap usedV(A_3) = \emptyset$

The functions *initials* gives the set of channels through which a given action may communicate first. The definition of this function is similar to that given in the CSP operational semantics presented in [21].

The above law requires that the set of channels through which  $A_3$  is initially prepared to communicate is included in the synchronisation set. Therefore,  $A_3$  cannot proceed independently. On the other hand,  $A_1$  does not communicate through channels in the synchronisation set. Therefore, it can proceed independently and necessarily goes first. We need, however, to impose a further restriction related to the state changes. The set of variables written by  $A_1$  and used by  $A_3$  cannot overlap, since in the parallel composition  $A_3$  acts on the initial value of the variables, and in the sequence, it acts on the values assigned by  $A_1$ .

An interesting law that relates parallelism and external choice is presented below. This is an exchange law that allows us to rearrange parallel actions; it is an important support for the task of splitting processes.

#### Law 614 (Parallelism/External Choice—Exchange)

$$(A_1 |\![ cs ]\!] A_2) \Box (B_1 |\![ cs ]\!] B_2) = (A_1 \Box B_1) |\![ cs ]\!] (A_2 \Box B_2)$$

provided  $A_1 |\![ cs ]\!] B_1 = A_2 |\![ cs ]\!] B_1 = Stop$

The choice on the left-hand action is for the parallel execution of  $A_1$  and  $A_2$ , or  $B_1$  and  $B_2$ . On the right-hand action, there is also the possibility of parallel execution of  $A_1$  and  $B_2$ , or  $B_1$  and  $A_2$ . The proviso, however, ensures that these choices lead to deadlock, so they are not a possibility.

In our case study, we also use well-known laws of hiding and recursion. Finally, we make use of some very simple unit and zero laws. These are all listed in Appendix A.

## 7 Case study

To illustrate our refinement strategy, we develop an implementation for the bounded, reactive, buffer introduced in Section 2 using the laws presented previously. The structure of the final implementation is a ring of cells with a central controller and a cached head. The entire development exercises two iterations of the strategy described in Section 3.

First, by data refinement, the bounded sequence is replaced by a cache that stores the head of the buffer when it is not empty, and a ring (circular array) that stores the tail of the original bounded buffer. The simulation relation was presented in Section 3. Next, the state changes associated with the input and output actions are decomposed into small units to deal with the cases in which the cache is updated and those in which the ring is updated. This is a first step towards isolating access to the ring. Afterwards, action refinements are carried out to separate those actions that access the ring from those that access the

other state components. Next, we decompose the original process into two: a controller and a centralised ring. This completes a first iteration of the strategy.

Through a second data refinement step, the centralised ring process is redesigned as a promotion of individual ring cells. In this case, no additional action refinement is necessary. Finally, we decompose the ring process into the interleaving of ring cell processes, each one storing a single value. This concludes the second iteration of the proposed strategy and the development of the entire case study. The following sections present the development in detail.

#### 7.1 Data refinement: a centralised ring buffer

Our first step is a data refinement, in which we introduce a *cache* and a *ring* to represent the internal state of the process *Buffer*. In Section 3 we presented the new concrete state, which we reproduce below.

```

process Buffer \cong begin

state

```

This new state requires a new description for the main action. To establish that our new *Buffer* is a refinement of that presented in Section 2, we prove that the new main action is related to that of the original process by a forwards simulation (Theorem 1). The retrieve relation *RetrBuffer* from Section 3 is reproduced below.

$RetrBuffer \cong [BufferState; CBufferState | buff = (1 .. size) \triangleleft (\langle cache \rangle \cap ((bot - 1) \ll ring))]$

Instead of proposing a new action from scratch, we consider the schema actions and rely on the fact that forwards simulation distributes through the action constructors (laws of Section 4). The new actions have the same structure as the original ones, but use the new schema actions.

The first schema action is the initialisation *BufferInit*. Initially, the buffer is empty and so has size zero; for the concrete initialisation, we choose some suitable values for *top* and *bot*.

$CBufferInit \cong [CBufferState' \mid size' = 0 \land bot' = 1 \land top' = 1]$

To prove that this new initialisation is related to *BufferInit* by forwards simulation, we need to apply Law 41, which considers schema actions. In this case, however, the provisos are simplified because initialisation schemas do not include the state components that represent the before state and have true as precondition. We actually obtain the standard proviso for refinement of initialisations in Z. All we have to prove is that

```

\forall BufferState; CBufferState; CBufferState' \bullet

RetrBuffer \land CBufferInit \Rightarrow (\exists BufferState' \bullet RetrBuffer' \land BufferInit)

```

This is a simple proof: the one-point rule, and the fact that  $(\emptyset \triangleleft s) = \langle \rangle$  for any sequence s, can be used to reduce  $\exists CBufferState' \bullet RetrBuffer' \land BufferInit$  to true. As this is on the right-hand side of the implication above, the proof-obligation is discharged.